# Research in Optoelectronics (A)

## 2010 Reprints of **Professor Larry A. Coldren** and Collaborators

ECE Technical Report 10-01 Department of Electrical & Computer Engineering University of California, Santa Barbara

# Research in Optoelectronics (A)

Reprints published in 2010 by

## **Professor Larry A. Coldren**

and Collaborators

Published as

Technical Report # ECE 11-01

of

The Department of Electrical & Computer Engineering

The University of California

Santa Barbara, CA 93106

Phone: (805) 893-4486 Fax: (805) 893-4500 E-mail: coldren@ece.ucsb.edu http://www.ece.ucsb.edu/Faculty/Coldren/home.htm

### Introduction:

Articles published by Professor Coldren's group in 2010 are contained in this volume. Any journal or conference publication in which Prof. Coldren was named as a co-author is included. The majority of these works also have originated from proposals generated within Coldren's group, but a few are due to efforts that originated elsewhere and were supported by Coldren and his group members. As in recent years the work has a focus on III-V compound semiconductor materials as well as the design and creation of photonic devices using these materials—mostly diode lasers and photonic integrated circuits (PICs). The work spans efforts from basic materials and processing technology, through device physics, design, and formation, to their characterization within systems environments.

The reprints have been grouped into three areas: **I. Photonic Integrated Circuits; II. Vertical-Cavity Surface-Emitting Lasers & MBE; and III. Fabrication Technology & Photonic Crystals.** Most of the work is in the first area, which has been further subdivided into *A. High Performance PICs; B. RF-Photonics; C. Programmable Lattice Filters; and D. Optical-Phase-Locked-Loops, Mode Locking, and Injection Locking.* In nearly every project the work requires efforts in materials research, device physics, device design, process development, device fabrication, and device characterization. Most students are deeply involved in several, if not all, of these efforts, so our graduates tend to be known for their "bandwidth."

The work was performed with funding from several grants from industry and government, some gift funds from industry, and support from the Kavli Endowed Chair in Optoelectronics and Sensors. Several projects were funded by the MTO Office of DARPA, one was supported by ONR, and the industries involved included Ziva Corp. and Rockwell-Collins.

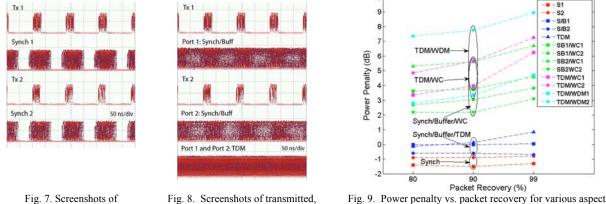

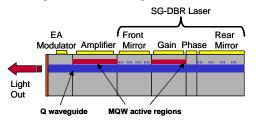

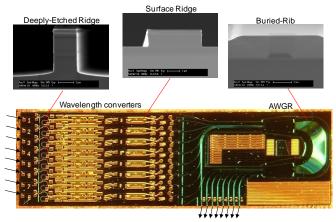

The first group of reprints (*IA*.) summarizes our work on *High-Performance PICs*. Notably all of the papers are INVITED, either directly by the journal or as invited conference talks in major international venues. All also center about the photonic integration technology we have originated, which incorporates our widely-tunable Sampled-Grating Distributed-Bragg-Reflector (SGDBR) Laser. The highlight for the past two years has been a single-chip 8 x 8 crossbar switch that uses eight wavelength converters integrated together with an arrayed-wavelength-grating-router (AWGR)—work done in collaboration with Prof. Blumenthal's group.

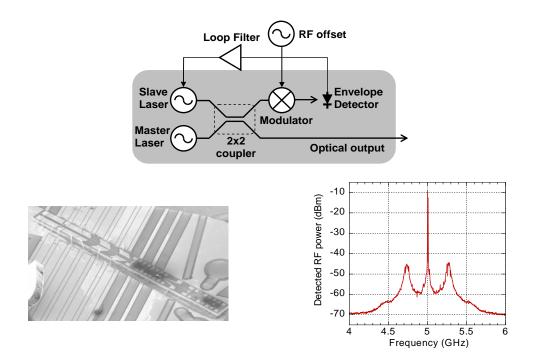

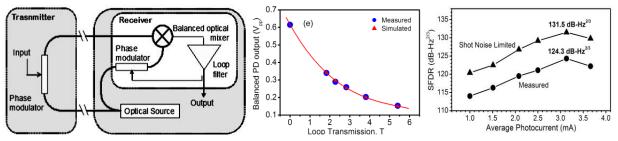

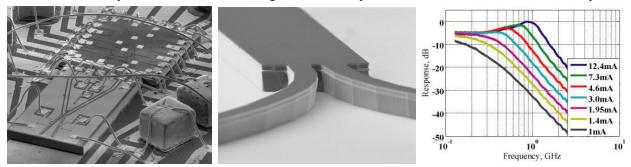

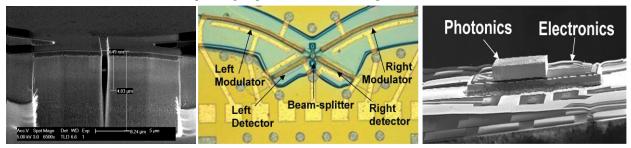

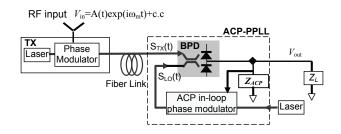

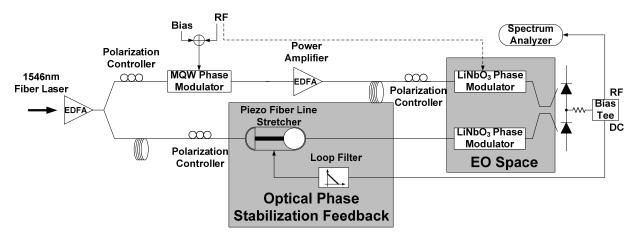

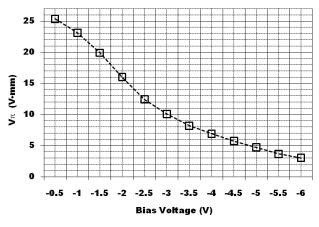

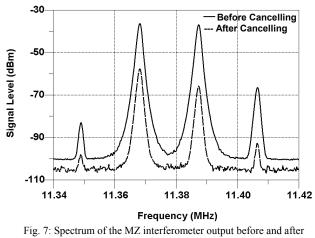

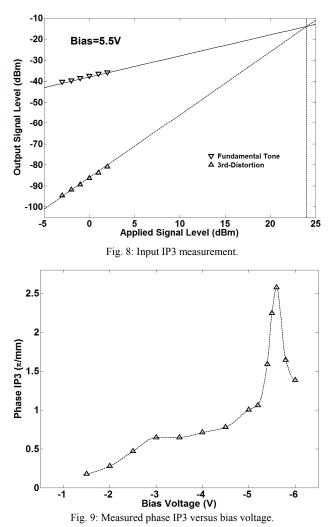

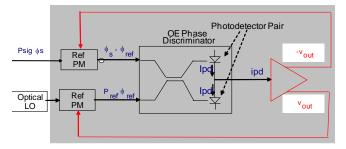

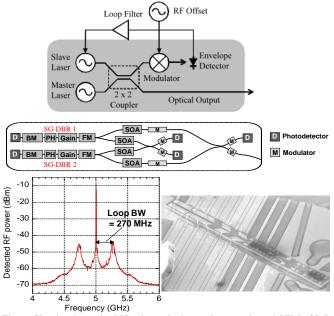

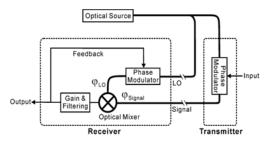

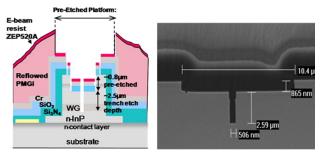

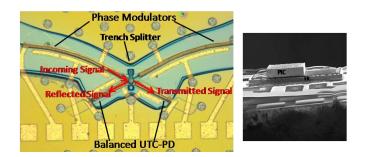

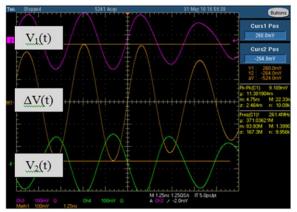

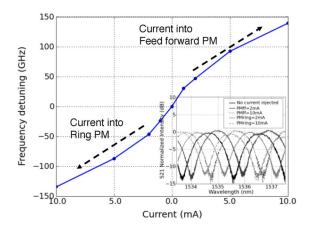

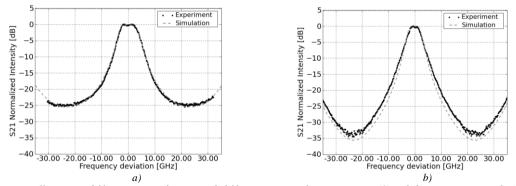

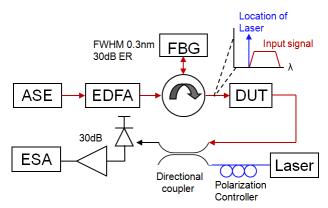

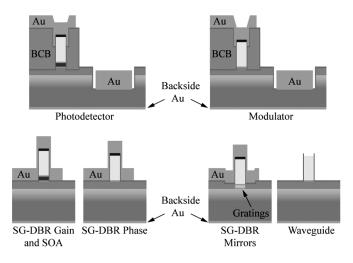

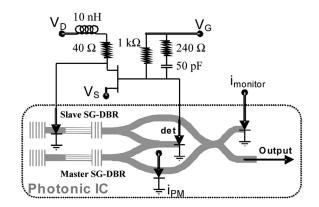

The Second group of papers (*IB*.) focuses on RF or analog photonics—techniques to transmit high-frequency analog information over optical fiber without distortion. Four papers, including one invited and one plenary paper, summarize results that have been obtained, primarily from our DARPA-PHORFRONT project. In this case, the objective was to demonstrate a high-dynamic-range coherent receiver for phase-modulated optical signals. Our approach involved using feedback to a tracking optical phase modulator to 'subtract out' the incoming optical modulation, thus allowing a large modulation swing as well as using a fraction of the feedback signal as the receiver output. In the final phase

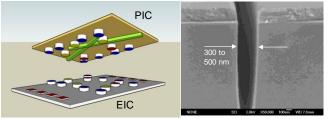

of the project, flip-chip bonding to an electronic chip (EIC) and etched-trench couplers were used to reduce the feedback delay so that the modulators could better track the difference signal and increase the bandwidth of the receiver. Figure 1 illustrates a schematic of the system along with results. All-optical receivers were also developed in which the current from the detectors were sufficient to drive the tracking modulators without any electronic amplification.

Figure 1. (top-left) Photo of PIC showing the phase modulators for the input signal and LO, the 50:50 trench splitter that combines equal portions of each to the balanced UTC-photo-detector (PD) pair; (top-center) SEM of trench; (top-right) schematic of PIC being flip-chipped to EIC. (bottom-left) Normalized rf output of PDs vs. frequency for several input powers—average photocurrent listed; (bottom-right) Two-tone distortion measurement—output power into a fundamental tone,  $f_1$ , together with IMD3:  $2f_2$ - $f_1$  level. Only 2.8 mA/PD is necessary for SFDR = 122 dB-Hz<sup>2/3</sup> using the feedback loop.

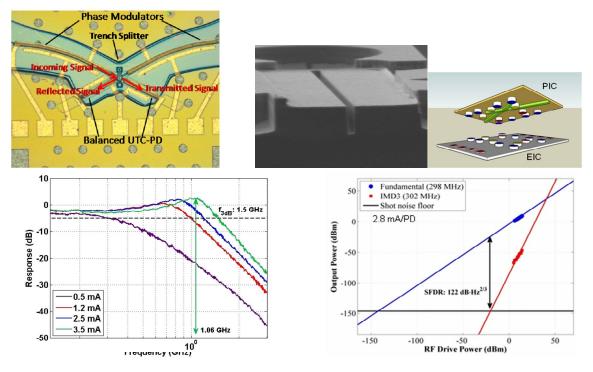

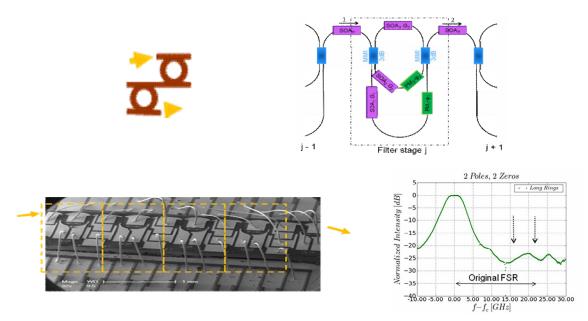

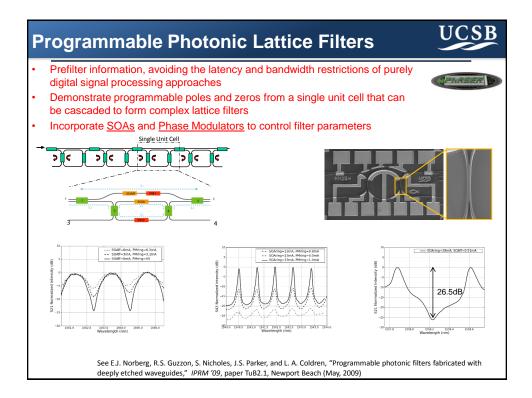

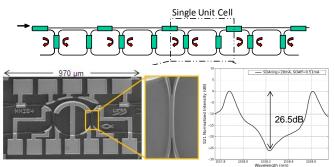

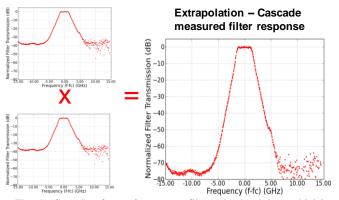

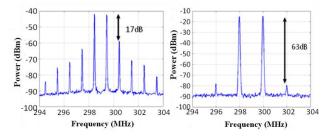

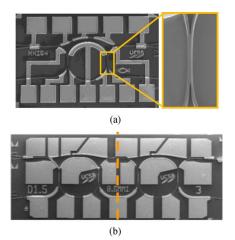

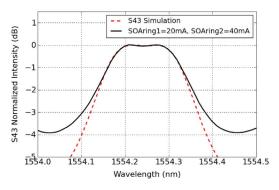

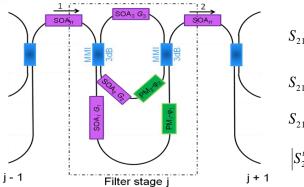

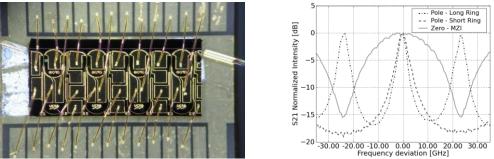

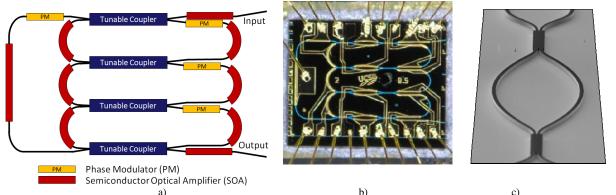

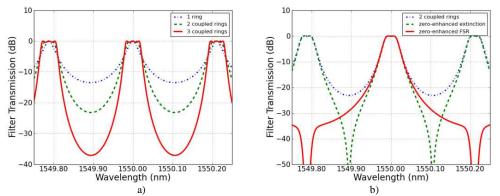

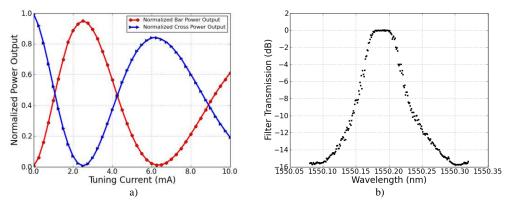

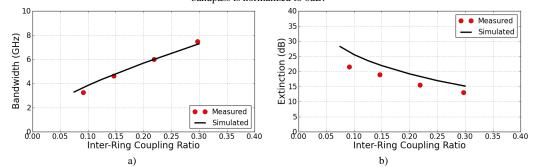

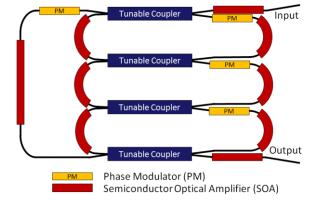

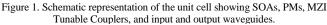

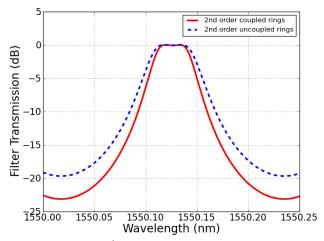

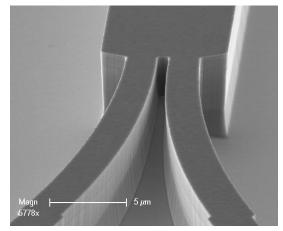

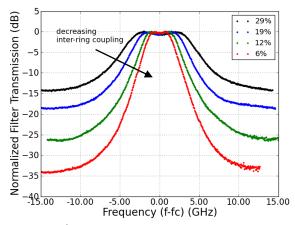

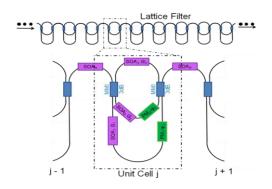

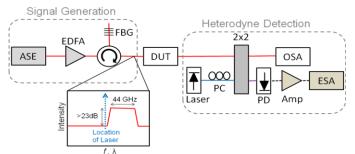

The work on *Programmable Lattice Filters (1C)* is summarized in five papers. Two basic approaches were pursued to build up higher order filters—(a) either cascade ring resonators using intermediate waveguides so that the resonances are uncoupled (no feedback between them), or (b) use a chain of coupled rings, in which the energy is shared amongst the rings. Figure 2 illustrates schematics of both schemes, the experimental layouts, and example results. This work was the result of work supported by the DARPA-PhASER project. As might be surmised by the placement of the various semiconductor optical amplifiers (SOAs) and phase modulators (PMs), these devices are very programmable in that many different filter configurations are possible, and the center wavelength and bandwidth are tunable. One possible application is to incorporate these in an rf photonic link to provide some adaptive pre-filtering prior to A/D conversion and Digital Signal Processing, thus enabling high-level decisions to be made rapidly and enabling more focused results with lower latency.

Figure 2a. (top) Concept and specific schematics of cascaded ring resonators. Top right shows element locations and indicates that rings of two different diameters are possible as well as operation in resonator or Mach-Zehnder mode. (bottom-left) SEM image of experimental chip showing four cascaded stages; (bottom-right) filter passband with two stages operated as resonators (poles or IIR mode) and two stages as Mach-Zehnders (zeros or FIR mode).

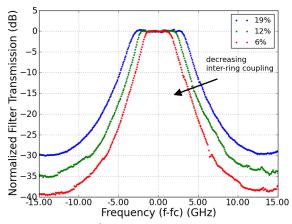

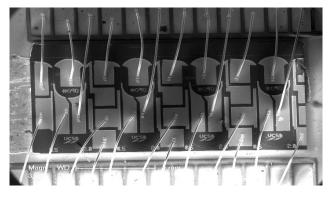

Figure 2b. (top) Concept and specific schematics of coupled ring resonators. Top right shows element locations and indicates a three-ring sub-element that also incorporates a Mach-Zehnder forward path. Variable interring couplers are key elements. (bottom-left) Photo of experimental chip; (bottom-right) filter passbands as the interring coupling is varied (inset) with Mach-Zehnder arm attenuated.

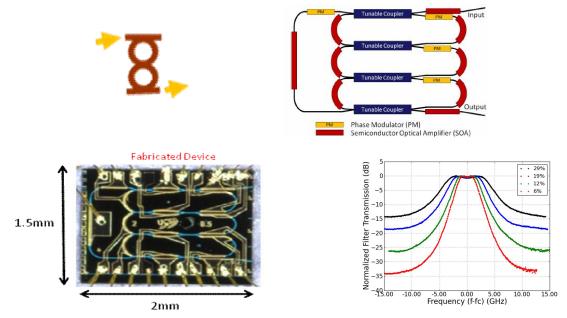

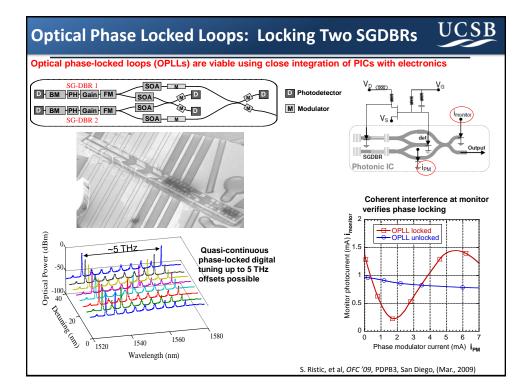

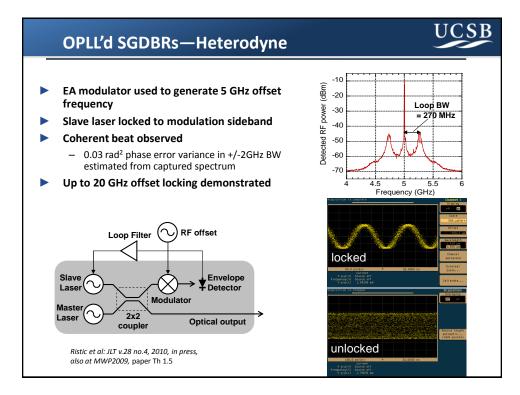

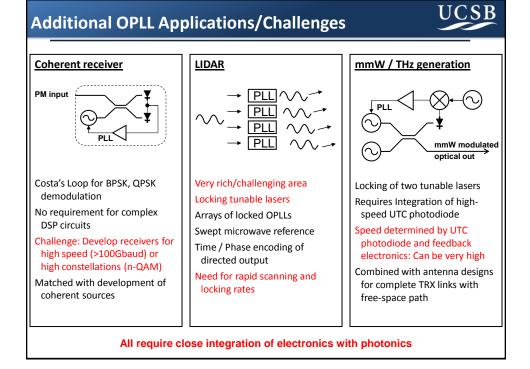

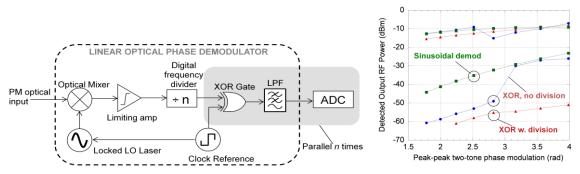

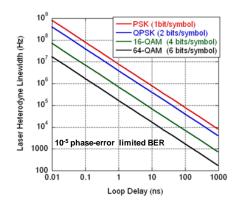

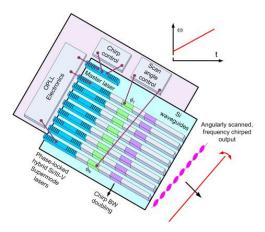

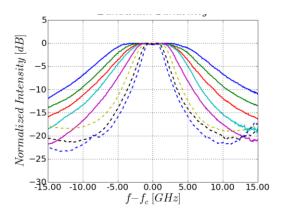

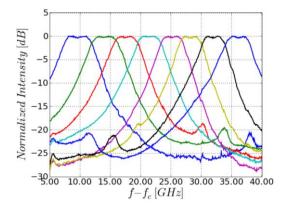

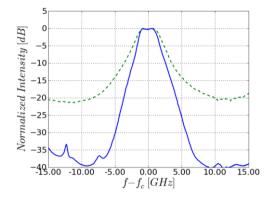

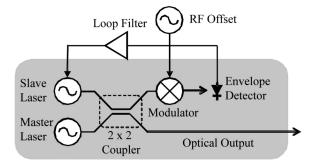

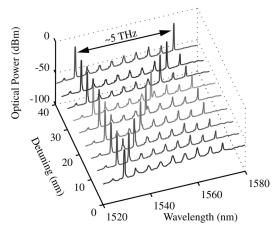

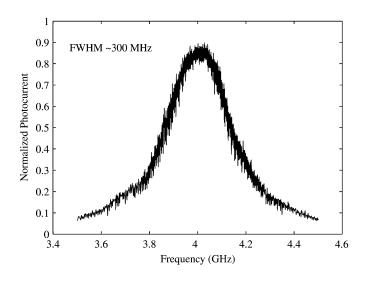

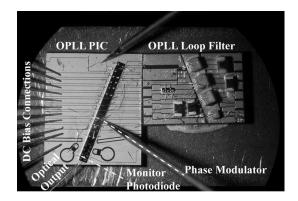

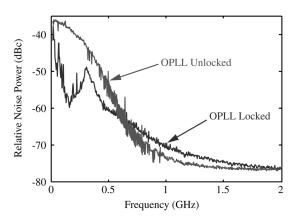

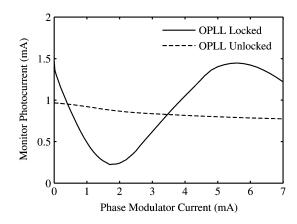

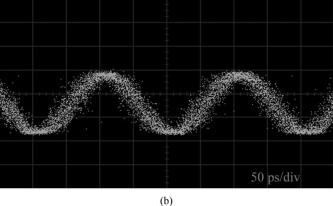

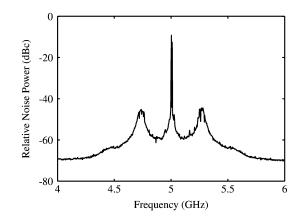

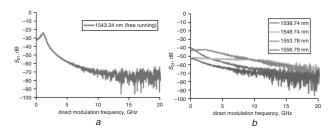

Section 1.D contains the results of efforts on Optical-Phase-Locked-Loops, Mode Locking, and Injection Locking. It contains an invited paper summarizing our efforts on homodyne and offset-heterodyne-locking of two monolithically-integrated SGDBR lasers

together with all of the photonic components necessary to phase lock them together on one chip. The cover of this volume illustrates results of 5 GHz heterodyne offset-locking. As can be seen, the detected difference frequency is relatively pure. The phase error variance of 0.03 rad<sup>2</sup> in +/-2GHz BW is estimated from the captured spectrum. Offset locking to 20 GHz was demonstrated. This work, initially funded by a DARPA seed project, laid some of the ground work for the proposal to the DARPA-CIPhER program that is now funded as 'PICO', together with a number of industry and university partners. This relatively large program on Photonic Integration for Coherent Optics (PICO), which contains a significant component on optical phase locked loops, will be at the center of much of the group's ongoing work. This program will also contain continuing work on mode-locking, initially funded by ONR, as well as injection locking.

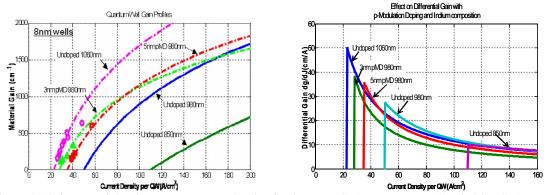

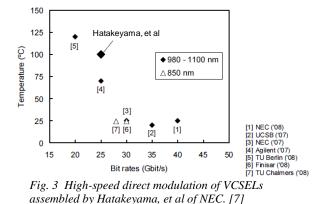

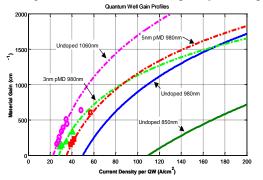

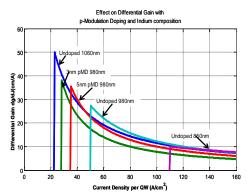

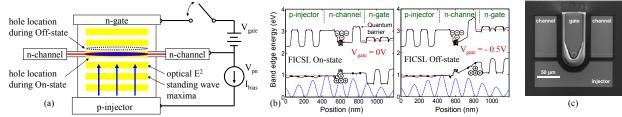

The publications in Section II on <u>Vertical-Cavity Surface-Emitting Lasers (VCSELs) & MBE</u> include recent work on high-speed VCSELs and novel three-terminal VCSELs. The invited paper summarizes our recent measurements that verify the tremendous advantages of using strained-layer quantum-well active regions because of their reduced transparency currents as well as increased differential gains. Figure 3 gives plots of gain and differential gain for various levels of strain (wavelength) vs current density to illustrate these points. The paper also references works that describe the enhanced reliability of devices with these materials. This work has been primarily funded by DARPA in the past, initially under the C2OI program. Coldren's group continues to work with highly-strained quantum-well VCSELs in the 1060 nm wavelength range for high-efficiency, high-speed data links.

Figure 3. (left) Material gain versus current density for 8 nm  $In_xGaAs$  quantum wells clad by GaAs except in the GaAs well (*x*=0) case, where it is clad by  $Al_{0.2}GaAs$ . Peak photoluminescence is given instead of *x*. Also included are p-type modulation-doped (*x*=0.2, or 980 nm) wells. (right) Differential gain, dg/dJ; in theory the relaxation resonance frequency and potential modulation bandwidth is proportional to the square root of this. As can be seen, 1060 nm wells promise more than twice the inherent modulation bandwidth at less than a quarter of the current compared to GaAs wells (for a nominal gain ~ 300-500 cm<sup>-1</sup> in each well).

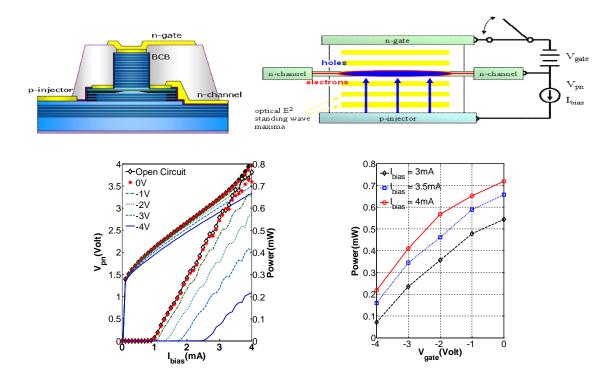

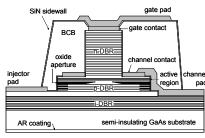

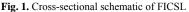

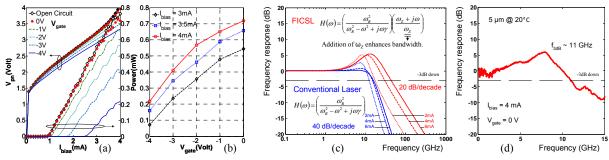

Figures 4 and 5 introduce two new three-terminal VCSEL structures that have been researched in Prof. Coldren's group. The first (Fig. 4) uses a third 'field-effect' terminal to separate holes and electrons as well as modulate the confinement factor in the active region. Because it is capacitively-coupled to the charge in the active region, only displacement current flows in this modulated terminal, and in principle, the voltage swing on can be quite low (<< 1 V). The initial results verify the basic physics, although more

work is needed to obtain the hoped-for results. Modeling indicates that it may be possible to send data at much higher rates with this new device configuration without resorting to costly and high-power-consuming external modulators. Support for these efforts has been coming from DARPA, NSF, and an STTR with Ziva Corp.

Figure 4. (top-left) Schematic of 3-terminal Field-Induced Charge-Separation Laser (FICSL) VCSEL cross section; (top-right) Equivalent circuit—dc current flows from p-injector (substrate) to n-channel, and the n-gate modulates the overlap of the holes and electrons in the channel via a field effect. No conduction gate current flows due to a quantum barrier. (bottom-left) PIV curves as a function of gate voltage—it is higher than necessary because of unnecessary resistance in the top mirror (n-gate); (bottom-right) modulation of output power at several constant channel currents.

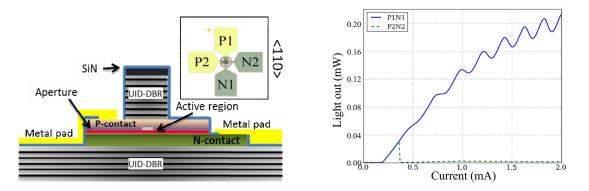

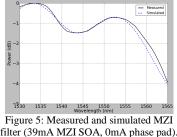

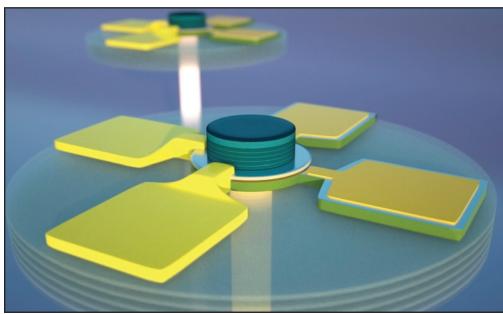

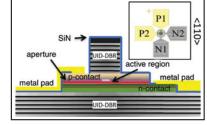

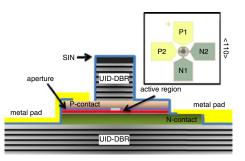

Figure 5 shows initial results for a VCSEL that uses the third terminal to modulate polarization. Actually, the third terminal is just a second current injection terminal, but as the first, it injects current in a somewhat lateral direction, but orthogonal to the first, so that the electron momentum direction can be slightly switched. This alters the gain for one polarization mode relative to the other and promotes the observed polarization switching. Greater than 21 dB extinction is observed, and the threshold current density is relatively low. This work has been done in collaboration with and under the support of an SBIR with Ziva Corp. Use of dual polarization sources can effectively double the data rate, and they can also be used in specialized sensor applications.

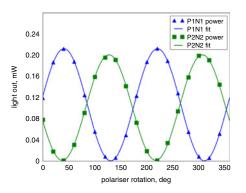

Figure 5. Schematic and results from polarization-modulated VCSEL. Current is applied either to electrodes P1-N1 or P2-N2 to force current to flow into the active region from the sides in one of two orthogonal directions. Although the electron k-vector is still predominately vertical near the bandedge in a quantum-well, this injection provides a slight bias on the in-plane component to be aligned preferentially along these directions, and the gain is very sensitive to this.

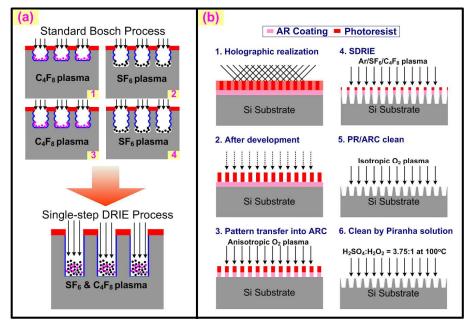

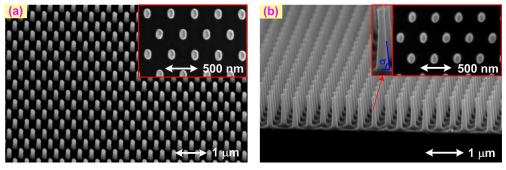

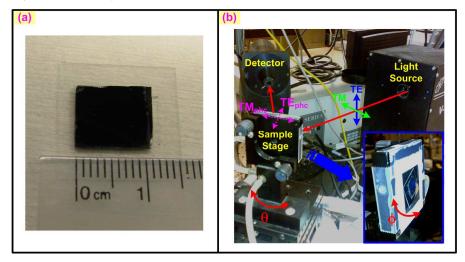

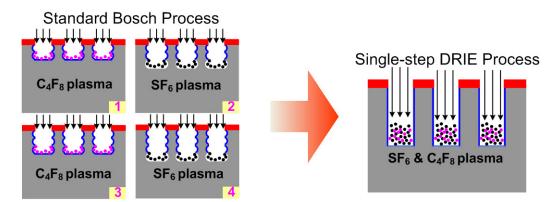

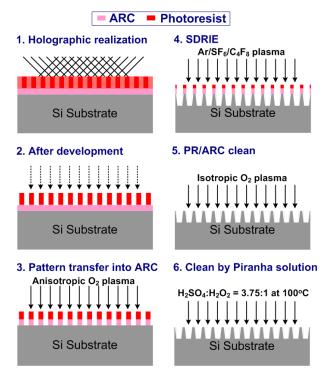

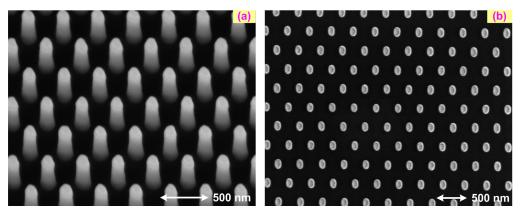

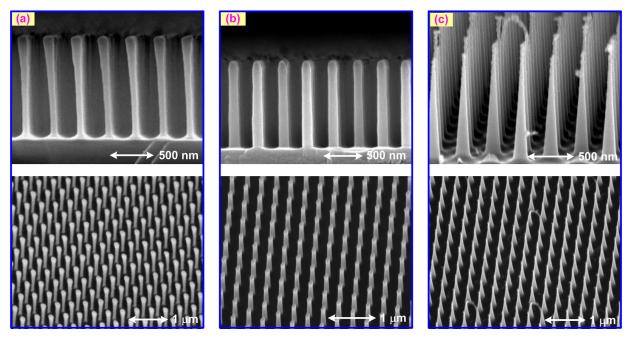

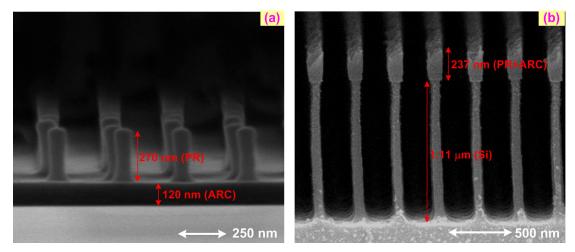

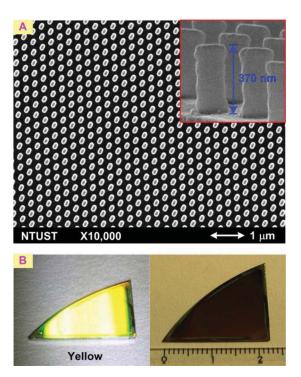

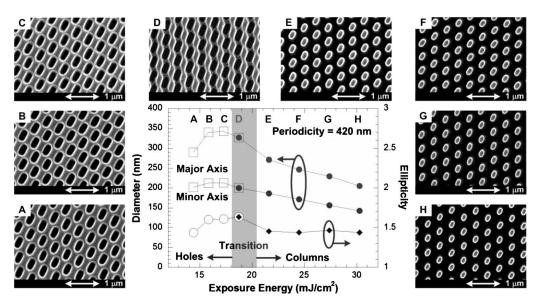

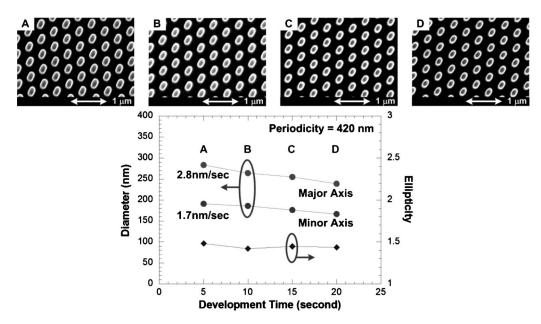

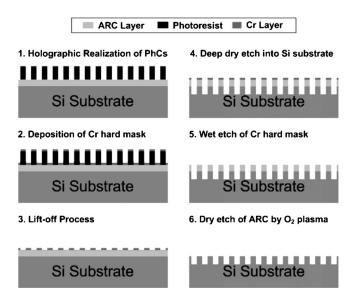

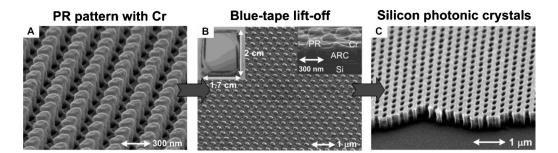

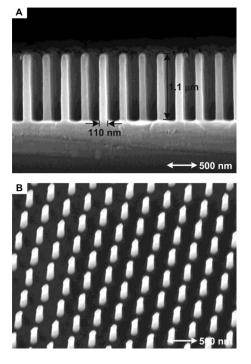

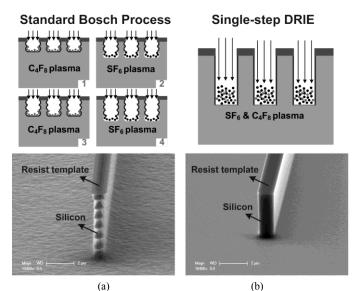

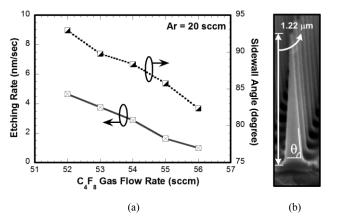

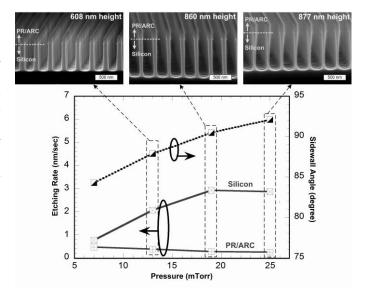

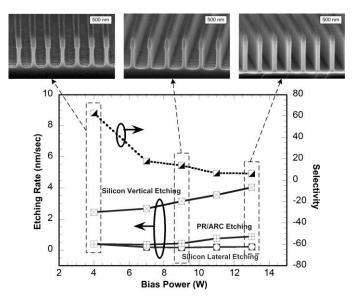

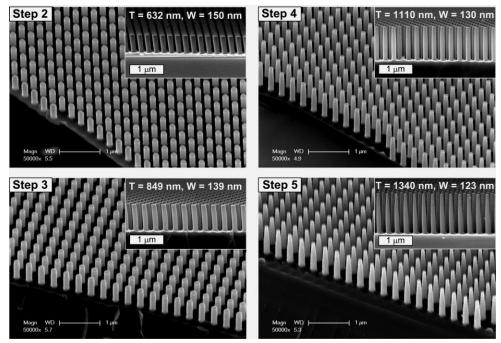

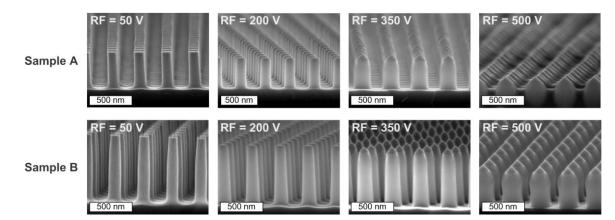

The publications in Section III, <u>Fabrication Technology & Photonic Crystals</u>, were all led by Y.-J. Hung, a visiting PhD student from Prof. S.-L. Lee's group at NTUST, Taiwan. Needless to say, Mr. Hung was a very productive and valuable addition to Prof. Coldren's group during his stay as is evidenced by the five papers he published in 2010. His work focused on developing an array of basic fabrication techniques for photonic crystals as well as many other photonic ICs. In fact, he developed several other useful technologies, such as multilayer anti-reflection coatings, that are not documented in the listed publications. It is also interesting to note that Prof. Lee was a former outstanding PhD student in Prof. Coldren's group some years ago.

Back Row: Chad Althouse, John Parker, Erik Norberg, Chin-Han Lin, Ashish Bhardwaj, Leif Johansson, Sasa Ristic, Uppili Krishnamachari Front Row: Weihua Guo, Jeannine Roson, Rob Guzzon, Professor Larry Coldren, Abi Sivananthan, Mingzhi Lu, Yan Zheng, Pietro Binetti

## **Professor Coldren's Group**

## I. <u>Researchers</u>

| A. Bhardwaj    | Visiting Scientist, UCSB                                    |

|----------------|-------------------------------------------------------------|

| Pietro Binetti | Postdoctoral Scholar, UCSB                                  |

| Weihua Guo     | Assistant Project Scientist, UCSB                           |

| Yung-Jr Hung   | Visiting Student from National Taiwan University of Science |

|                | and Technology, UCSB                                        |

| L. Johansson   | Associate Research Engineer, UCSB                           |

| S. Ristic      | Postdoctoral Scholar, UCSB                                  |

## II. <u>Students</u>

| C. Althouse       | Ph.D. Program                              |

|-------------------|--------------------------------------------|

| Y. Chang          | Ph.D. Program, now at Kaai Inc             |

| C. Chen           | Ph.D. Program, now at NTT Photonics Lab    |

| M. Dummer         | Ph.D. Program, now at Vixar Inc.           |

| R. Guzzon         | Ph.D. Program                              |

| U. Krishnamachari | Ph.D. Program                              |

| CH. Lin           | Ph.D. Program                              |

| M. Lu             | Ph.D. Program                              |

| S. Nicholes       | Ph.D. Program, now at Aurrion              |

| E. Norberg        | Ph.D. Program                              |

| J. Parker         | Ph.D. Program                              |

| A. Sivananthan    | Ph.D. Program                              |

| A. Tauke-Pedretti | Ph.D. Program, now at Sandia National Labs |

| Y. Zheng          | Ph.D. Program                              |

|                   |                                            |

## III. <u>Staff</u>

| D. Cohen | Principal Development Engineer, reports to Prof Nakamura |

|----------|----------------------------------------------------------|

| J. Roson | Center Assistant, OTC                                    |

## Collaborators

I. <u>Faculty</u>

| D. Blumenthal | UCSB |

|---------------|------|

| J. Bowers     | UCSB |

| M. Rodwell    | UCSB |

## II. <u>Researchers</u>

| E. Burmeister  | Ciena                                                |

|----------------|------------------------------------------------------|

| HF. Chou       | Post Doctoral Researcher, UCSB (Bowers)              |

| J. English     | Principal Development Engineer, UCSB Materials       |

| P. Herczfeld   | Professor, Drexel University                         |

| A. Jackson     | Project Scientist, UCSB ECE                          |

| J. Klamkin     | Staff Member, Lincoln Labs                           |

| SL. Lee        | Professor, National Taiwan University of Science     |

|                | and Technology                                       |

| Y. Li          | Prof. University of Massachusetts at Dartmouth       |

| M. Masanovic   | Associate Project Scientist, UCSB (Blumenthal)       |

| YT. Pan        | Researcher, National Taiwan University of Science    |

|                | and Technology                                       |

| H. Poulsen     | Research Scientist, UCSB (Blumenthal)                |

| B.J. Thibeault | Project Scientist (Rodwell)                          |

| R. Wang        | Researcher, University of Massachusetts at Dartmouth |

## Collaborating Students

| UCSB (Blumenthal) |

|-------------------|

| UCSB (Blumenthal) |

| UCSB (Bowers)     |

| UCSB (Blumenthal) |

| UCSB (Blumenthal) |

| UCSB (Blumenthal) |

|                   |

| M. Piels     | UCSB (Bowers)     |

|--------------|-------------------|

| A. Ramaswamy | UCSB (Bowers)     |

| B. Stamenic  | UCSB (Blumenthal) |

### **Table of Contents:**

## I. Photonic Integrated Circuits

## IA. High Performance PICs

S.C. Nicholes, M. Masanovic, B. Jevremovic, E. Lively, L.A. Coldren, and D. Blumenthal, "An 8x8 InP monolithic tunable optical router (MOTOR) packet forwarding chip," *Journal of Lightwave Tehcnology*, **28**, (4), pp. 641-650 (February 15, 2010) INVITED PAPER

Larry Coldren, "High performance photonic integrated circuits (PICs)," *OFC/NFOEC Proc*, paper no. OWD1, San Diego, CA (March 21-25, 2010) INVITED TUTORIAL

J.P. Mack, K.N. Nguyen, J.M. Garcia, E.F. Burmeister, M.M. Dummer, H.N. Poulsen, B. Stamenic, G. Kurczveil, K. Hollar, L.A. Coldren, J.E. Bowers, and D.J. Blumenthal, "Asynchronous 2×2 optical packet synchronization, buffering, and forwarding," *OFC/NFOEC Proc*, paper no. OThN1, San Diego, CA (March 21-25, 2010) INVITED PAPER

S. C. Nicholes, M. L. Mašanovič, B. Jevremovič, E. Lively, L. A. Coldren, and D. J. Blumenthal, "Integration technologies for an 8x8 InP-based monolithic tunable optical router with 40Gb/s line rate per port," *IPRM Proc*, paper no. WeA3-1, Kagawa, Japan (May 31 – June 1, 2010) INVITED PAPER

S.C. Nicholes, M.L. Mašanović, B. Jevremović, E. Lively, L.A. Coldren, and D.J. Blumenthal, "Largescale photonic integration for advanced all-optical routing functions," *Integrated Photonics Research Proc*, paper no. ITuC1, Monterey, CA (July 25-28, 2010) INVITED PAPER

## *IB. RF-Photonics*

L.A. Johansson, U. Krishnamachari, A. Ramaswamy, J. Klamkin, S. Ristic, H.-F. Chou, L.A. Coldren, M.J. Rodwell, and J.E. Bowers, "Linear coherent optical receivers," *OFC/NFOEC Proc*, paper no. OThF5, San Diego, CA (March 21-25, 2010) INVITED PAPER

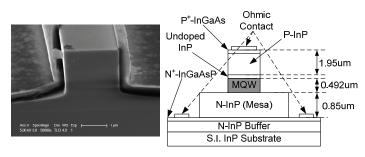

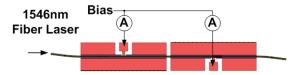

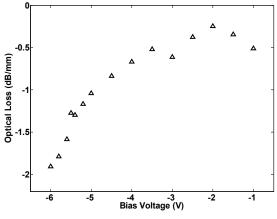

R. Wang, A. Bhardwaj, S. Ristic, L. A. Coldren, J. Bowers, P. Hercfeld, and Y. Li, "Highly linear InP phase modulator for high dynamic range RF/photonic links," *Int. Microwave Symposium Proc*, paper no. WE3C-1, Anaheim, CA (May 23-28, 2010)

L.A. Coldren, "Photonic integrated circuits for microwave photonics," *Proc. MWP*, paper no. WE1-1, Montreal, Canada (October 5-9, 2010) PLENARY PAPER

U. Krishnamachari, S. Ristic, A. Ramaswamy, L.A. Johansson, C. –H. Chen, J. Klamkin, M. Piels, A. Bhardwaj, M. Rodwell, J.E. Bowers, and L.A. Coldren, "An ultra-compact integrated coherent receiver for high linearity RF photonic links," *Proc. MWP*, paper no. WE2-5, Montreal, Canada (October 5-9, 2010)

## IC. Programmable Lattice Filters

E.J. Norberg, R.S. Guzzon, S.C. Nicholes, J.S. Parker, and L.A. Coldren, "Programmable photonic lattice filters in InGaAsP/InP," *IEEE Photonics Technology Letters*, **22**, (2), pp. 109-111 (January 15, 2010)

E.J. Norberg, R.S. Guzzon, J.S. Parker, and L.A. Coldren, "Programmable photonic filters from monolithically cascaded filter stages," *Integrated Photonics Research Proc*, paper no. ITuC3, Monterey, CA (July 25-28, 2010)

R.S. Guzzon, E.J. Norberg, J.S. Parker, and L.A. Coldren, "Highly programmable optical filters integrated in InP-InGaAsP with tunable inter-ring coupling," *Integrated Photonics Research Proc*, paper no. ITuC4, Monterey, CA (July 25-28, 2010)

R.S. Guzzon, E.J. Norberg, J.S. Parker, L.A. Johansson, and L.A. Coldren, "Monolithically integrated programmable photonic microwave filter with tunable inter-ring coupling," *Proc. MWP*, paper no. WE2-4, Montreal, Canada (October 5-9, 2010)

E.J. Norberg, R.S. Guzzon, J.S. Parker, L.A. Johansson, and L.A. Coldren, "A monolithic programmable optical filter for RF-signal processing," *Proc. MWP*, paper no. FR1-2, Montreal, Canada (October 5-9, 2010)

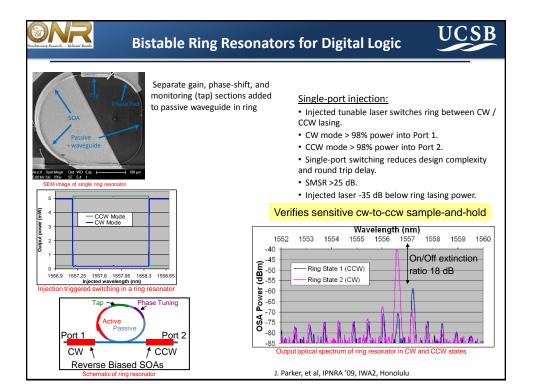

## ID. Optical-Phase-Locked-Loop, Mode Locking, and Injection Locking

S. Ristic, A. Bhardwaj, M. Rodwell, L. Coldren, and L. Johansson, "An optical phase-locked loop photonic integrated circuit," *Journal of Lightwave Technology*, **28**, (4), pp. 526-538 (February 15, 2010) INVITED PAPER

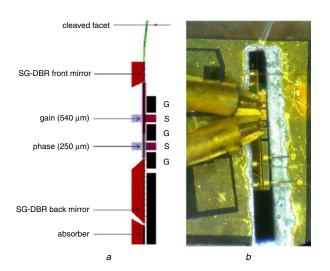

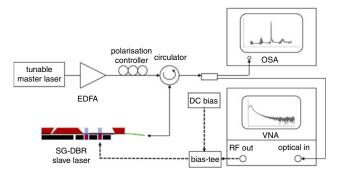

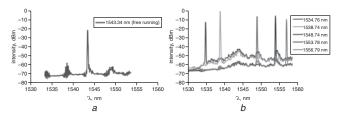

A. Bhardwaj, S. Ristic, L. Johansson, C. Althouse, and L.A. Coldren, "Direct modulation bandwidth enhancement of a strongly injection-locked SG-DBR laser," *Electronics Letters*, **46** (5), pp. 362-363 (March 2010)

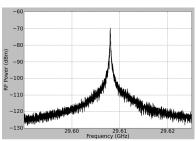

J.S. Parker, A. Bhardwaj, P.R.A. Binetti, Y. Hung, C. Lin, L.A. Coldren, "Integrated 30GHz passive ring mode-locked laser with gain flattening filter," *Proc. ISLC*, paper no. PD1, Kyoto, Japan (September 26-30, 2010)

## II. Vertical-Cavity Surface-Emitting Lasers (VCSELs) & MBE

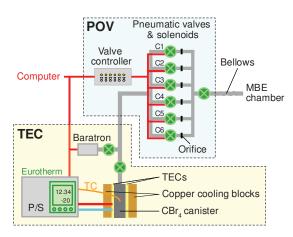

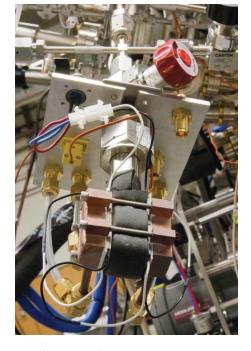

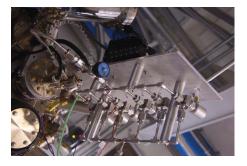

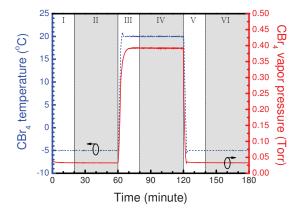

Y.-C. Chang, Y. Zheng, J. H. English, A. W. Jackson, and L. A. Coldren, "Wide-dynamic-range, fast-response CBr4 doping system for molecular beam epitaxy," *J. Vac. Sci. Technol. B*, **28** (3), pp. C3F10-C3F15 (May 2010)

L.A. Coldren, Y.-C. Chang, Y.Zheng, and C.-H. Lin, "Efficient sources for chip-to-chip to box-to-box communication within data centers," *Photonics Society Summer Topical Proc*, paper no TuD2.1, Playa Del Carmen, Mexico (July 19-21, 2010) INVITED PAPER

C.-H. Lin, Y. Zheng, M. J. W. Rodwell, L. A. Coldren, "First demonstration of modulation via fieldinduced charge-separation in VCSELs," *Proc. ISLC*, paper no. PD2, Kyoto, Japan (September 26-30, 2010)

Y. Zheng, C.-H. Lin and L.A. Coldren, "VCSELs take control," *Electronics Letters*, **46**, (24), pp.1580 (November 25, 2010)

Y. Zheng, C.-H. Lin and L.A. Coldren, "Large extinction ratio and low threshold dual intra-cavity contacted polarisation switching VCSELs," *Electronics Letters*, **46**, (24), pp. 1619-1620 (November 25, 2010)

## III. Fabrication Technology & Photonic Crystals

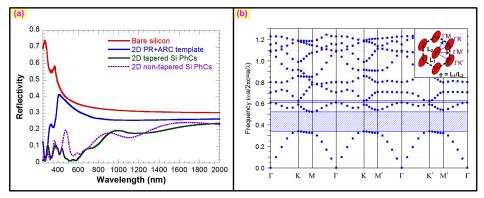

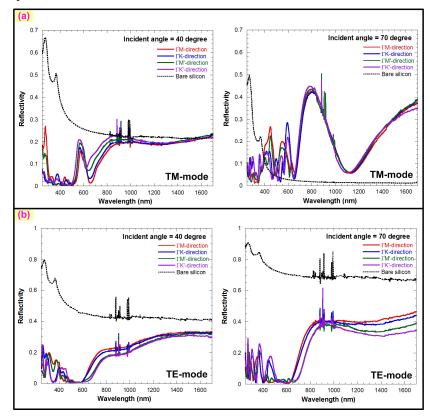

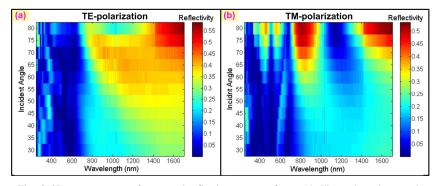

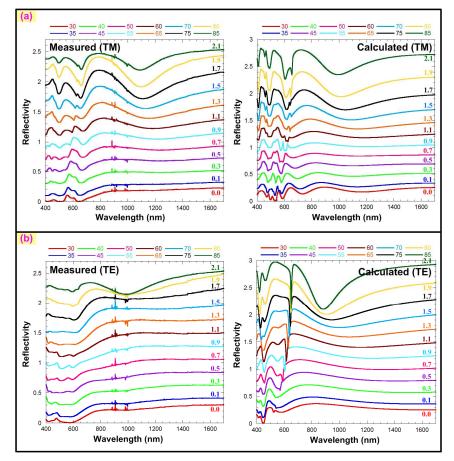

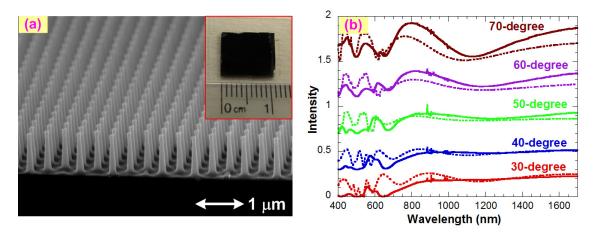

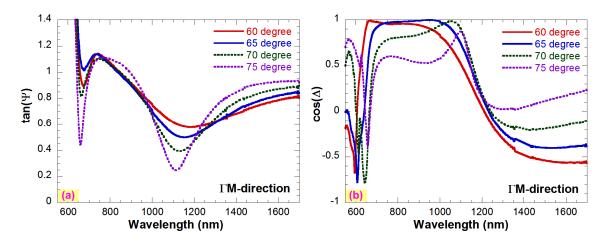

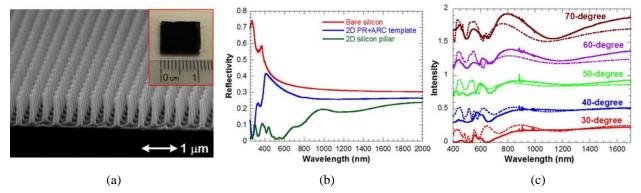

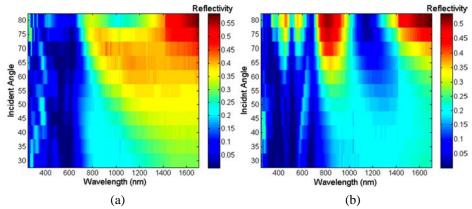

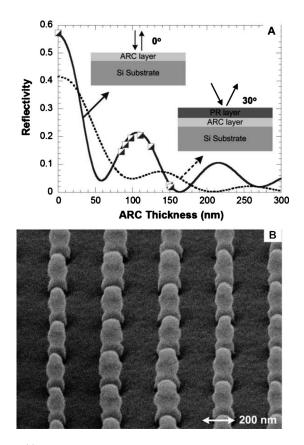

Y.-J. Hung, S.-L. Lee and L. A. Coldren, "Deep and tapered silicon photonic crystals for achieving anti-reflection and enhanced absorption," *Optics Express* **18**, 6841 (March, 2010)

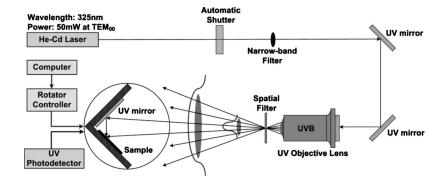

Y.-J. Hung, S.-L. Lee, B. J. Thibeault, and L. A. Coldren, "Realization of silicon nanopillar arrays with controllable sidewall profiles by holography lithography and a novel single-step deep reactive ion etching," *MRS Proc*, Spring Meeting, 1258-Q14-02, San Francisco, (April, 2010)

Y.-J. Hung, S. -L. Lee, B.J. Thibeault, and L.A. Coldren, "Antireflection and enhanced absorption in tapered silicon photonic crystals," *Integrated Photonics Research Proc*, paper no. IWEC6, Monterey, CA (July 25-28, 2010)

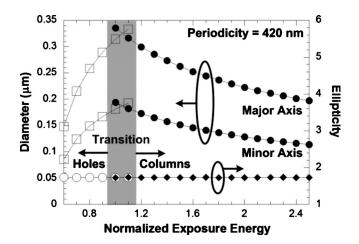

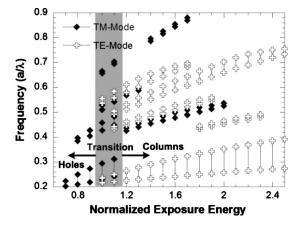

Y.-J. Hung, S.-L. Lee, Y.-T. Pan, B.J. Thibeault, and L.A. Coldren, "Holographic realization of hexagonal two dimensional photonic crystal structures with elliptical geometry," *J. Vac. Sci. and Tech B*, **28**, (5), pp. 1030-1038, (September 27, 2010)

Y. -J. Hung, S. -L. Lee, B.J. Thibeault, and L.A. Coldren, "Fabrication of highly-ordered silicon nanowire arrays with controllable sidewall profiles for achieving low surface reflection," *J. Sel. Topics. Quantum Electron.*, **PP**, (99), pp. 1-9 (October 17, 2010)

# I. Photonic Integrated Circuits

A. High Performance PICs

## An 8 × 8 InP Monolithic Tunable Optical Router (MOTOR) Packet Forwarding Chip

Steven C. Nicholes, Milan L. Mašanović, *Member, IEEE*, Biljana Jevremović, Erica Lively, *Student Member, IEEE*, Larry A. Coldren, *Fellow, IEEE, Fellow, OSA*, and Daniel J. Blumenthal, *Fellow, IEEE, Fellow, OSA*

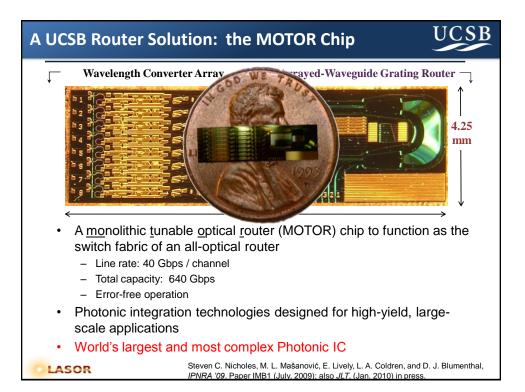

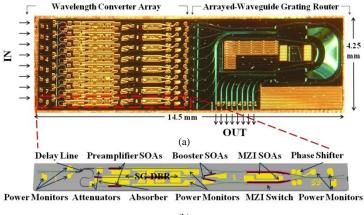

Abstract-In this paper, we demonstrate single-channel operation of the first InP monolithic tunable optical router (MOTOR) chip designed to function as the packet forwarding engine of an all-optical router. The device has eight-input and eight-output ports and is capable of 40-Gb/s operation per port with bit-error rates below 1E-9. MOTOR integrates eight wavelength-tunable differential Mach-Zehnder semiconductor optical amplifier (SOA) wavelength converters with preamplifiers and a passive  $8 \times 8$  arrayed-waveguide grating router. Each wavelength converter employs a widely tunable sampled-grating distributed Bragg reflector (DBR) laser for efficient wavelength switching across the C band and other functions required for 40-Gb/s wavelength conversion. Active and passive regions of the chip are defined through a robust quantum well intermixing process to optimize the gain in the wavelength converters and minimize the propagation losses in passive sections of the chip. The device is one of the most complex photonic integrated circuits (PICs) reported to date, with dimensions of 4.25 mm  $\times$  14.5 mm and more than 200 functional elements integrated on-chip. We demonstrate single-channel wavelength conversion and channel switching with this device using  $2^{31} - 1$  pseudorandom bit sequence (PRBS) data at 40 Gb/s. A power penalty as low as 4.5 dB was achieved with less than 2-W drive power per channel.

*Index Terms*—Arrayed-waveguide grating router (AWGR), photonic integrated circuits (PIC), quantum-well intermixing (QWI), wavelength converter.

### I. INTRODUCTION

DVANCED photonic integrated circuits (PICs) in InP are a critical technology to manage the increasing bandwidth demands and core functions of next-generation optical networks [1]–[4]. The integration of many of the discrete functions required in optical networks into a single device provides a reduction in system footprint and optical losses due to the elimination of fiber coupling junctions between components, and an increase in overall reliability. Many key network components such as transceivers [5], wavelength converters [6]–[9], optical

Manuscript received May 15, 2009; revised July 20, 2009. First published August 18, 2009; current version published February 05, 2010. This work was supported by the DARPA MTO and the U.S. Army under the DOD-N LASOR Project (W911NF-04-9-0001).

S. C. Nicholes is with the Department of Materials, University of California, Santa Barbara, CA 93106 USA (e-mail: snicholes@engineering.ucsb.edu).

M. L. Mašanović, B. Jevremovic, E. Lively, L. A. Coldren, D. J. Blumenthal are with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106 USA (e-mail: mashan@ece.ucsb.edu; biljana@ece.ucsb.edu; elively@ece.ucsb.edu; coldren@ece.ucsb.edu; danb@ece.ucsb.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JLT.2009.2030145

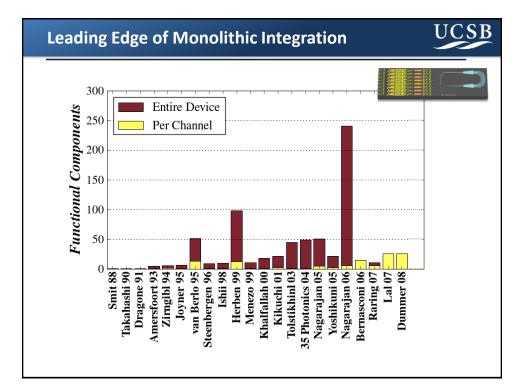

cross connects [10], add-drop multiplexers [11], and channel selectors [12] have already been realized in InP via monolithic integration. While the potential benefits of creating larger, higher functionality PICs have long been suggested, there are still very few demonstrations of PICs with more than 50 integrated components [2], [13].

Large scale integration in silicon-based integrated circuits has led to exponential growth in that industry and tremendous performance gains with a reduction in costs to the consumer. Robust design and manufacturing techniques that will enable highyield production of large scale PICs are thus required to realize similar performance and cost improvements in the photonics industry [3]. Such efforts have been underway for several years, and the benefits of large scale integration are now being seen commercially with the recent report by Infinera of plans to deploy a 400-Gb/s PIC transmitter with more than 300 optical functions in live networks [14].

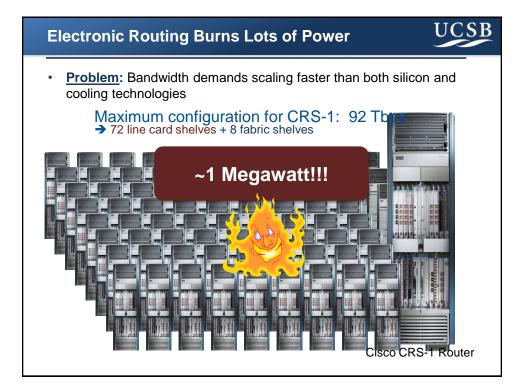

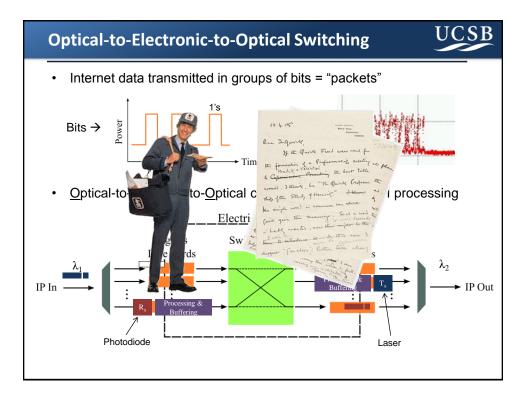

All-optical routing is a potential avenue in which large scale PICs could play a revolutionary role [15]. By moving the functions of dynamic wavelength conversion and routing to the optical layer, it may be possible to ease the increasing power consumption demands associated with scaling electronic-based routers to higher data rates [16]. For instance, discrete all-optical wavelength converters have been reported that entirely eliminate the need for power-hungry optical-to-electrical (O/E) and electrical-to-optical (E/O) data conversion [6]–[9]. While these demonstrations of wavelength conversion without O/E/O conversions are promising, the realization of a competitive all-optical alternative to electronic routers is still limited by challenges associated with optical buffering [17].

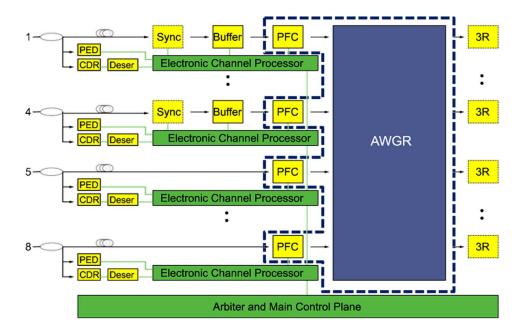

In [18], a label-switched all-optical router (LASOR) with the ability to process 40-Gb/s packets was proposed. This router architecture (Fig. 1) enables synchronization and buffering of input packets in the optical domain, and provides a means to write the input data onto a new wavelength for wavelength-selective routing. While each functional block of the router could be realized with a discrete PIC, the performance of this system in terms of reliability, optical coupling losses, and overall footprint can be significantly improved via large scale monolithic integration.

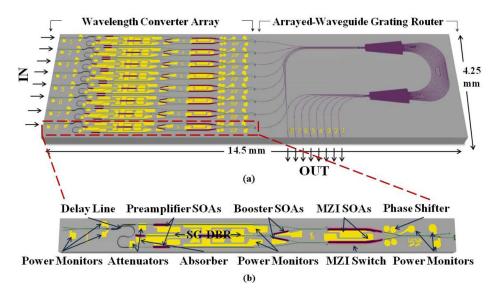

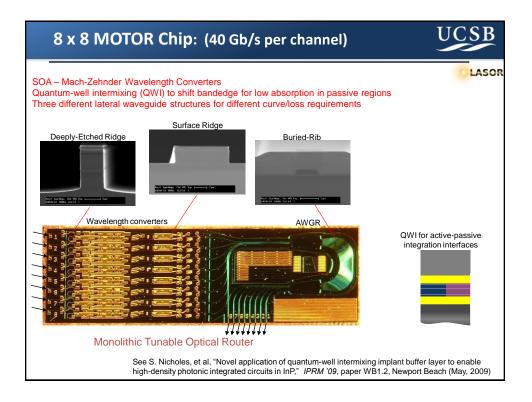

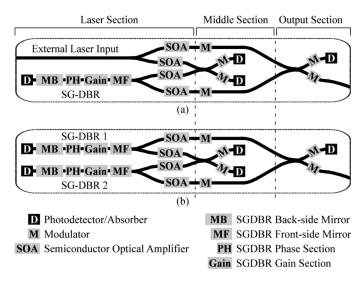

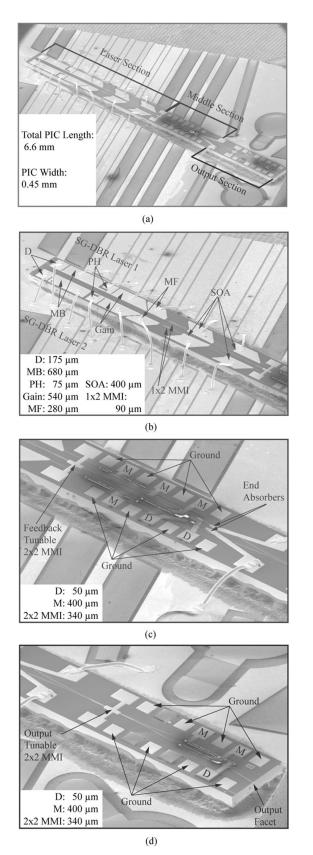

In this work, we combine the wavelength conversion and passive routing elements of LASOR shown in Fig. 1 into a single InP chip to demonstrate a monolithic tunable optical router (MOTOR) that serves as the packet-forwarding engine of an all-optical router [Fig. 2(a)]. The eight-channel InP/In-GaAsP device operates at 40-Gb/s line rate per port giving a total potential data capacity of 640 Gb/s and integrates an array of eight tunable all-optical wavelength converters with a passive  $8 \times 8$  arrayed-waveguide grating router (AWGR).

Fig. 1. Overall LASOR architecture. Key to abbreviations: PED = payload envelope detection; CDR = clock data recovery; Deser = deserializer; Sync = synchronizer; WC = wavelength converter; AWGR = arrayed-waveguide grating router; <math>3R = retiming, reshaping, and reamplification. The dotted region represents the elements integrated in the MOTOR chip.

Fig. 2. (a) Schematic of overall MOTOR chip. (b) Expanded view of a single-input wavelength converter showing several key device elements.

The device represents one of the most complex InP PICs ever reported with more than 200 integrated functional elements on a single chip.

### II. DEVICE DESIGN AND OPERATION

### A. Wavelength Converter Array

The active core of the MOTOR chip contains an array of eight wavelength converters. The technology used to implement these wavelength converters must provide: 1) error-free high-speed operation at 40 Gb/s; 2) wide tunability across the C band; 3) a small footprint; and 4) low power consumption (i.e., no O/E/O conversions). Two popular monolithic approaches to achieve these goals with 40-Gb/s data rates involve carrier-modulation effects in nonlinear semiconductor optical amplifiers (SOAs) [6], [7] or field-modulation effects with a photodiode and a modulator [9]. While each approach has inherent advantages, the design and fabrication of field-modulation-based wavelength converters tends to be more complex than that of carrier-modulation-based devices because they require integrated resistors and more complex modulator structures [9]. In order to target high device yields, we use the simpler carrier-modulation approach in the MOTOR chip.

Because our wavelength converter design exploits nonlinear SOA within a Mach–Zehnder interferometer (MZI) as in [7], both cross-phase and cross-gain modulation effects are present. However, cross-phase modulation in the MZI is the method used to shape the output pulses from the device. A detailed view of a single-input MOTOR port is shown in Fig. 2(b). The input data signal to the chip depletes the carriers in a nonlinear SOA and changes the phase in one branch of an MZI. This phase change modulates the MZI and carves out the input data pattern onto a continuous wave (CW) source operating at the new wavelength. The overall speed of these devices is inherently limited by the carrier lifetime in the SOAs, so a differential delay line at the front end of the chip is included [7]. By time delaying the input data signal on one side of the MZI, it is possible to overcome the limitation of carrier recovery lifetime so that modulation of the MZI is governed by carrier depletion effects. The time delay is accomplished using an on-chip differential delay line before the inputs to the MZI. After the input data signal is split using a 50/50 multimode interferometer (MMI) splitter, the signals are sent to opposite branches of the MZI. The path length for one branch is increased relative to the other using a compact, tight bend radius waveguide section that adds about 11 ps of propagation delay. This delay time was chosen to simultaneously minimize the overall power penalty associated with wavelength conversion while keeping the delay line length as small as possible to minimize device footprint [19]. In general, improved performance can be achieved if the input power levels to each side of the MZI are slightly imbalanced [7], [20]. Because the path length of the inputs to the MZI differ (and hence the propagation losses differ), and because the observed splitting ratio of the fabricated MMI is sensitive to lithographic resolution, variable optical attenuators (VOAs) are included on each input line to the MZI to control the relative power levels in each branch.

The wide tunability of the wavelength converter is accomplished by incorporating a sampled-grating distributed Bragg reflector (SG-DBR) laser as the on-chip CW source. The laser consists of five sections: a 550- $\mu$ m active gain section, a 470- $\mu$  m front, a 910- $\mu$ m back tuning mirror, a short 100- $\mu$ m phase tuning pad, and a 175- $\mu$ m active absorber. About 40 nm of tuning is possible through the Vernier effect [21]. By biasing both the front and back mirrors during operation, it is possible to precisely tune to any of the allowed output wavelengths of the AWGR across the C band.

The MOTOR chip also integrates SOAs with three different functions. First, 285- $\mu$ m booster SOAs are used to amplify the SG-DBR output power after it is split by a 50/50 MMI splitter and before it is input into each branch of the MZI. Because the SG-DBR output power is already high, the booster SOAs are saturated but provide enough gain to overcome the halving in power from the MMI splitter. Second, nonlinear SOAs are required in the Mach-Zehnder for cross-phase and cross-gain modulation. These SOAs are >1000  $\mu$ m in length in order to reduce the carrier recovery time, which tends to decrease with increasing SOA length [20]. Finally,  $300-\mu m$  linear preamplifier SOAs are inserted before the input to the MZI to amplify the input data signal. It is crucial that these SOAs provide an optimal combination of high gain (to ensure that the input pulses have enough power to deplete the carriers in the MZI SOAs) and high saturation power (to avoid pattern dependent distortions that arise if the preamplifier SOAs are operated in the nonlinear regime).

One important consideration with this approach to wavelength conversion is the possibility of wavelength blocking.

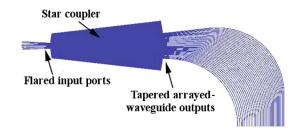

Fig. 3. Schematic view of the AWGR illustrating the flared input and tapered output waveguides.

Unlike the field-modulated wavelength converters of [9], it is not possible to convert back to the input wavelength with the differential MZI SOA wavelength converter because the input data signal exits the device from the same port as the converted signal. In a routing application, this means that the input frequency comb must be different than the output frequency comb and either a high- or low-pass filter would be required at the output to remove the original frequencies.

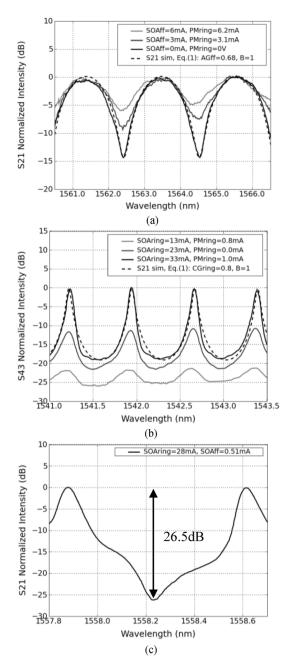

### B. Arrayed-Waveguide Grating Router

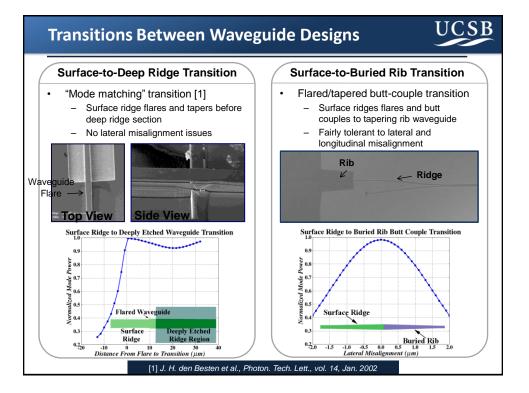

The output of the wavelength converter is connected to an AWGR, which passively routes the wavelength converted signal based on the new wavelength of the data (as set by the SG-DBR). Our design employs an  $8 \times 8$  configuration with 200-GHz channel spacing (to give a reasonable AWGR size), a center wavelength of 1550 nm, and a periodic output frequency response. The major source of loss in an AWGR is from imperfect coupling between the waveguides and the star couplers (or free propagation regions) [22]. To reduce these losses and improve coupling, our design employs flared and tapered waveguides at the star couplers (Fig. 3). The flares and tapers are 100  $\mu$ m long in order to minimize the excitation of higher order modes. The 2.2- $\mu$ m waveguide inputs to the star couplers are flared to 8.0  $\mu$ m and are spaced by 1.0  $\mu$ m. The 34 arrayed waveguides at the output of the star couplers taper from 8.25 to 2.2  $\mu$ m and are spaced by only 0.8  $\mu$ m. The overall size of the AWGR (not including the waveguides to the input star coupler and the waveguides from the output star coupler) is  $2.84 \text{ mm} \times 2.60 \text{ mm}.$

### **III. INTEGRATION PLATFORM**

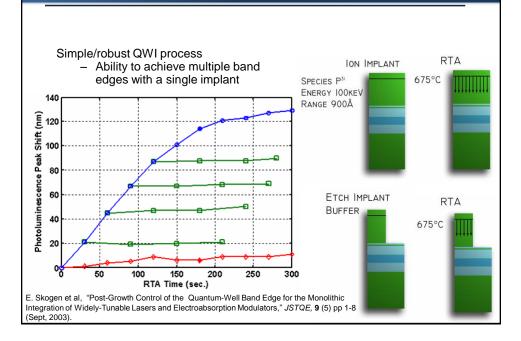

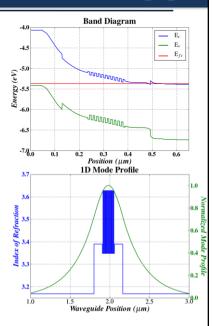

The integration platform used for the MOTOR chip should provide several key features: 1) high-gain regions for the SG-DBR laser and SOAs; 2) low-saturation-power (i.e., nonlinear) SOAs in the MZI; 3) high-saturation-power (i.e., linear) SOAs for preamplifiers; 4) efficient phase modulator regions for the MZI; and 5) low-loss waveguides for the AWGR and passive sections of the wavelength converters. Additionally, the integration platform should minimize the number of required regrowths and limit the overall fabrication complexity in order to maximize device yield. To meet these demands, we use an impurity-free quantum-well intermixing (QWI) process and a single, blanket *p*-type cladding regrowth.

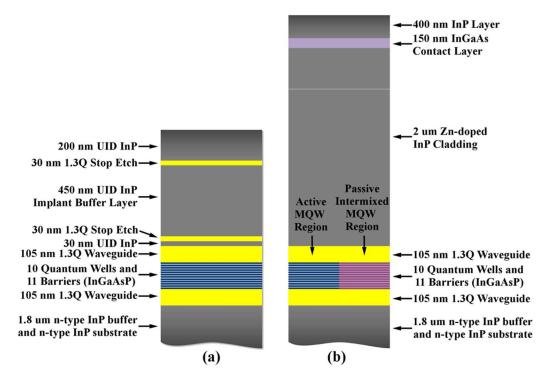

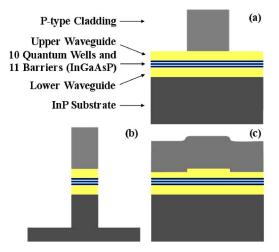

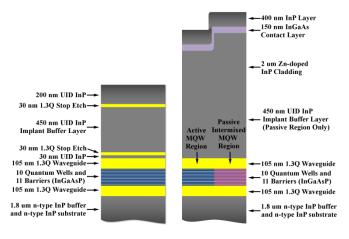

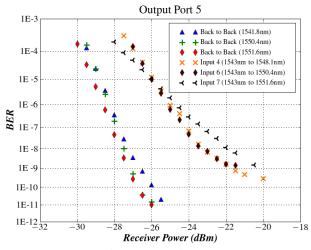

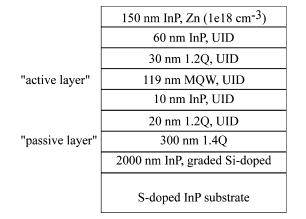

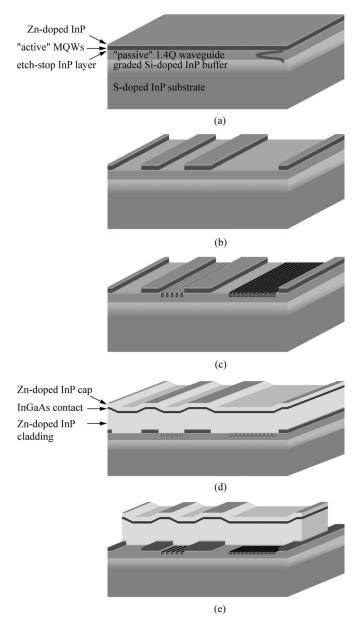

The initial base epitaxial layer structure [Fig. 4(a)] is grown by MOCVD on a sulfur-doped InP substrate. It is composed of ten 6.5-nm InGaAsP quantum wells under +0.9% compressive strain and eleven 8.0-nm InGaAsP barriers under -0.2% tensile

Fig. 4. (a) Initial base epitaxial growth structure. (b) Final growth structure showing both an as-grown active MQW region and an intermixed passive MQW region.

strain ( $\lambda_{\rm PL} = 1545$  nm). The multiple quantum well (MQW) stack is sandwiched by a 105-nm quaternary waveguide ( $\lambda_{\rm PL} =$ 1300 nm) on both sides to maximize the modal overlap in the MQWs, resulting in a  $\sim$ 13% optical confinement factor. The increased optical confinement provides high-gain regions for the booster SOAs and the gain section of the SG-DBR and low-saturation power regions for the nonlinear MZI SOAs. However, the decrease in saturation power due to high optical confinement limits the maximum possible unsaturated gain from the preamplifier SOAs. The base growth also incorporates an undoped InP buffer layer above the waveguide for QWI [23]. Passive device regions are defined by selectively implanting phosphorous into the undoped buffer layer above these regions. The implant creates point defects which are then diffused through the waveguide region using a rapid thermal anneal process in  $N_2$  at 675 °C. These vacancies and interstitials allow diffusion of the group V elements across the metastable well and barrier boundaries to reshape the compositional profile of the MQW region and blue shift the band edge from an as-grown  $\lambda_{\rm PL}$  of 1545 to 1420 nm. Because the passive regions still contain quantum wells, it is possible to realize more efficient phase shifters in the MZI region than would be available with only bulk waveguide. MQWs provide a greater refractive index change for a given injected current density than bulk material because of the step-like density of states of a 2-D system [24]. In practical terms, this means that less current (and hence a lower drive power) is required to tune the phase of the MZI to a normally closed (noninverting) or open (inverting) state.

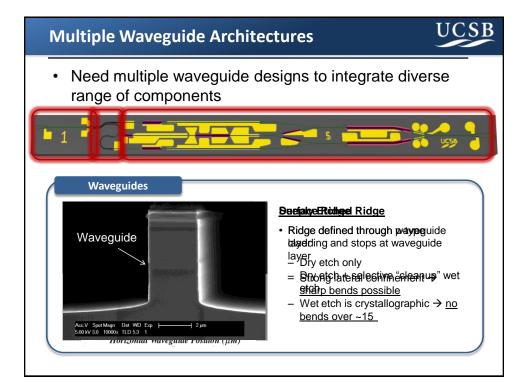

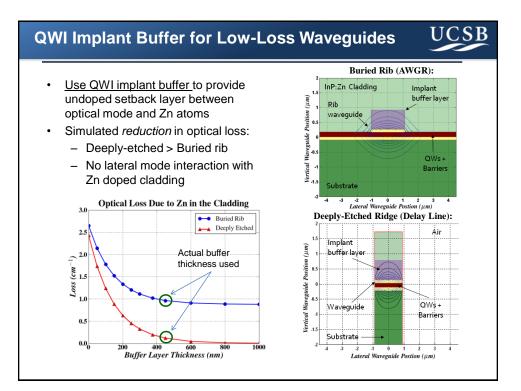

Following QWI, the implant buffer layer is removed across most of the sample by wet etching. In the passive regions of the differential delay line and the AWGR, however, the buffer layer is not removed in order to provide an undoped setback

Fig. 5. Waveguide architectures used in the MOTOR chip: (a) surface ridge waveguide; (b) deeply etched waveguide; and (c) buried rib waveguide.

layer between the waveguide and the subsequent cladding. As described in [25], this helps to reduce optical loss from free carrier absorption due to the Zn dopant used in the cladding layer. The epitaxial structure is completed by a simple, blanket *p*-type regrowth [Fig. 4(b)]. A 150-nm heavily Zn-doped InGaAs layer is included in the regrowth for Ohmic *p*-type contacts. Using a single regrowth step reduces fabrication complexity and should have a positive impact on device yield. However, the Zn doping profile with this approach must be optimized to provide efficient active diode performance without detrimentally increasing passive propagation losses from free carrier absorption [26]. To address this inherent tradeoff, our cladding regrowth with Zn doping.

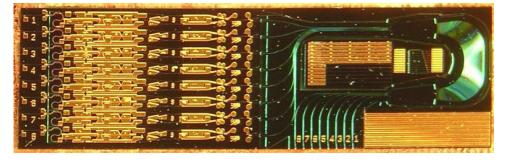

Fig. 6. Photograph of fabricated MOTOR chip. The chip is soldered to a large copper block and electrodes are directly probed. Miscellaneous test structures are contained in the center of the AWGR region, but these components are not used during the operation of the device.

Due to the elevated growth temperature, some Zn diffuses toward the waveguide, creating the desired *p-i-n* junctions of the device. The thickness of this undoped regrowth layer (typically ~30–50 nm) is calibrated to ensure that the Zn doping concentrations within the waveguide are as low as possible. To reduce the loss further, additional pre- and postgrowth techniques are employed. Prior to growth as mentioned above, the undoped QWI buffer layer is left in the delay line and AWGR region to push the Zn away from the waveguide. After growth, a proton implant is utilized to passivate some of the activated Zn atoms above the waveguide, thus reducing passive losses to a more manageable level of about 1.9 cm<sup>-1</sup> for a surface ridge waveguide.

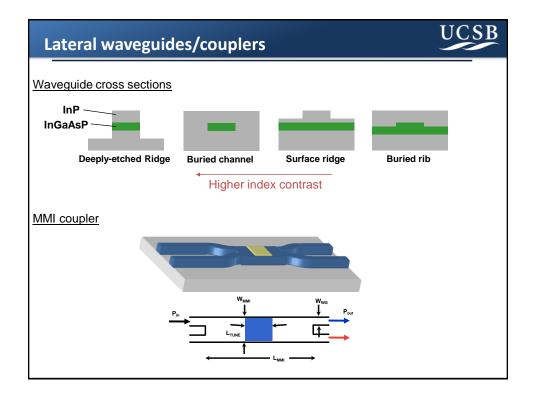

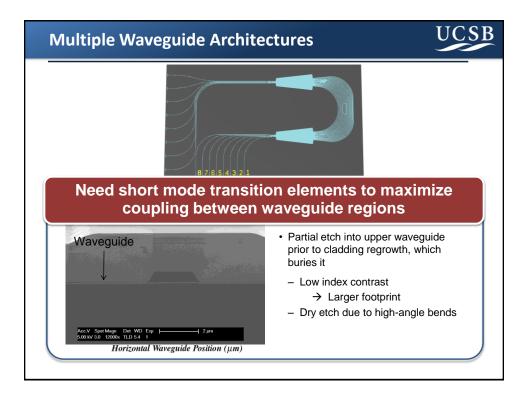

Three different ridge waveguide architectures are used in MOTOR (Fig. 5). A surface ridge that stops at the top of the waveguide layer is utilized for all active components and most passive regions of the wavelength converters. This design offers a simple fabrication approach through a combination of dry and selective wet etching. Although the selective nature of the wet etch provides precise control of the etch depth, its crystallographic nature leads to detrimental undercutting of waveguides with an angle greater than about  $15^{\circ}$  off  $[\overline{1} \ 10]$  toward the [110]direction. The device also employs a high-contrast, deeply etched waveguide region for the compact differential delay line in the wavelength converter. This region is partially defined during the dry etch step of the surface ridge waveguide to eliminate misalignment between the two sections. It is then protected with a resist mask during the wet etch of the surface ridge. An SiO<sub>2</sub> liftoff process is subsequently used to open the delay line region and a second dry etch through the waveguide is performed. Last, a buried rib waveguide is created in the AWGR region by dry etching through the implant buffer layer and 70 nm of the upper waveguide prior to the cladding regrowth, which consequently buries the structure. Because no selective wet etch is used, this approach can provide waveguides in the AWGR region that can be bent a full 180° to achieve a more compact structure.

### IV. EXPERIMENTAL SETUP

The fabricated MOTOR chip (shown in Fig. 6) was soldered to a copper block for testing. Because this is not an ideal heat sinking configuration, the device was maintained at 16 °C during operation using a thermoelectric cooler (TEC) to reduce thermionic emission of carriers from the MQW region of the device. Wire bonding was not practical given the size of

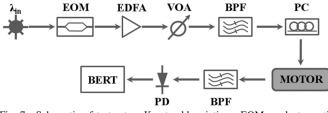

Fig. 7. Schematic of test setup. Key to abbreviations: EOM = electro-optic modulator; EDFA = erbium-doped fiber amplifier; VOA = variable optical attenuator; BPF = band-pass filter; PC = polarization controller; PD = photodiode; BERT = bit error rate tester.

the device so all electrodes were directly probed. Light was coupled to and from the chip using lensed fiber. The response of the AWGR was characterized using on-chip sources (i.e., MZI SOAs and the SG-DBR) and coupling the output from each port to an optical spectrum analyzer (OSA). Wavelength conversion and routing functions of the MOTOR chip were tested under single-channel operation with pseudorandom bit sequence (PRBS)  $2^{31} - 1$  RZ data at 40 Gb/s. The input data signal is generated with a modulated external cavity tunable laser source, amplified with an erbium-doped fiber amplifier (EDFA) and filtered with a 5-nm filter. Because the device employs compressively strained MQWs, it is TE-polarization sensitive and a polarization controller is used to rotate the input signal to a TE orientation. Although the AWGR provides on-chip filtering at most wavelengths, the fiber-coupled output signal from the device is also filtered with an external 5-nm filter for cases in which the wavelength of the original input signal might correspond to an allowed output wavelength of the AWGR. The output was then transmitted to a preamplified receiver. Bit error rate (BER) measurements were made using a 40-Gb/s SHF BERT. A schematic of the test setup is shown in Fig. 7. Back-to-back BER measurements were made using all test elements in this setup with the MOTOR chip removed.

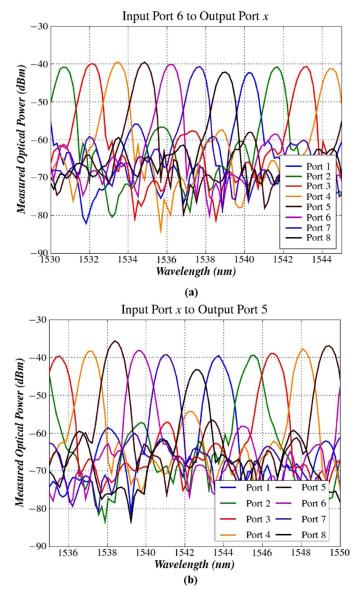

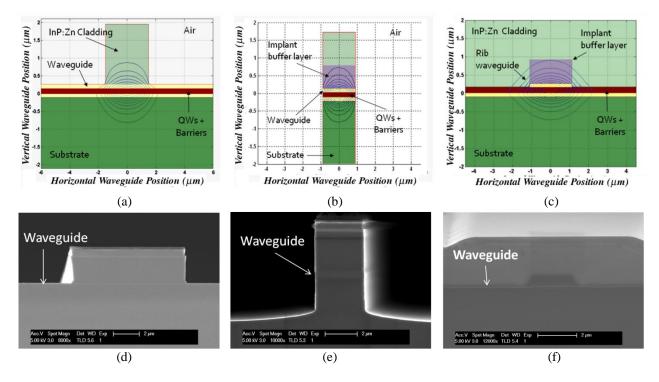

### V. ARRAYED-WAVEGUIDE GRATING ROUTER RESULTS

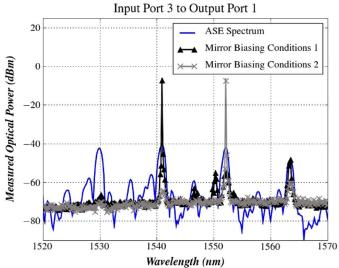

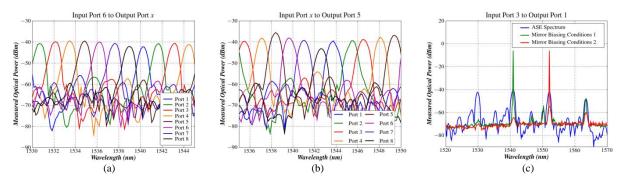

The performance of the AWGR was first characterized by forward biasing the MZI SOAs on a single-input wavelength converter to generate amplified spontaneous emission (ASE) and the spectral response from each egress port was measured. Fig. 8(a) shows a well-defined free spectral range (FSR) of approximately 11.1 nm from the AWGR and a single-channel crosstalk between -15.8 and -20.9 dB across all output ports (measured at the center wavelength of the ASE peak). Next, the pair of MZI SOAs in each input wavelength converter were

Fig. 8. Output ASE response of the integrated AWGR: (a) measured optical output from all output ports using input wavelength converter #3; (b) measured optical output from output port #2 using each input wavelength converter.

biased pair-by-pair at a constant bias level and the resulting spectra were measured from a single-output port [Fig. 8(b)]. Although some difference in power level is expected between center and outer ports of an AWGR, this figure illustrates that the performance of each input port varies, likely due to fabrication variations across the device. In general, all but one input port show crosstalk values in excess of -15.6 dB. Input port #8 only demonstrates a crosstalk of -12.3 dB, most likely due to a waveguide imperfection within this port. This will translate into a reduction in performance for port #8 relative to the other input wavelength converters.

To verify the performance of the device in terms of tunability, the SG-DBR was used in conjunction with the booster SOAs, which were forward biased to provide gain to the CW signal from the SG-DBR. Because the MZI SOAs are in the path between the SG-DBR and the AWGR, they were also biased in order to allow the signal to propagate without being absorbed.

Fig. 9. Lasing spectra for different biasing conditions using the SG-DBR of input wavelength converter #3 superimposed on the ASE spectrum generated by forward biasing just the MZI SOA pair in that channel, all measured from output port #1.

By changing the biasing conditions on the front and back mirrors of the SG-DBR, the laser can be tuned to any of the allowed output wavelengths of a given port in order to achieve full channel switching. Fig. 9 shows the resulting spectra for two different mirror biasing conditions from a single-input wavelength converter to a single output. In this configuration, we measured output powers approaching -5 dBm.

Given the current architecture of our device, it is not possible to directly measure the insertion loss of the AWGR without cleaving it from the wavelength converter array. To make a reasonable estimate of the total throughput loss between the wavelength converters and the output, we measured the total power (including ASE) directly at the exit of the wavelength converter in an integrated power monitor diode with the SG-DBR, booster SOAs, and MZI SOAs forward biased at typical operating conditions. (We estimated the quantum efficiency of this power monitor by measuring the absorbed power in this pad when coupling a CW signal backward through the device from the exit of the AWGR into the wavelength converters and then comparing it to the power measured in the long MZI SOAs which should absorb all the incoming light.) The total power out of the AWGR was coupled into an output fiber and measured in an OSA. Assuming 4–5 dB of coupling loss to the fiber, the total power loss through the AWGR was estimated to be  $\sim$ 8–10 dB. It is important to note that this loss also includes the loss associated with transitioning from the surface ridge waveguide of the wavelength converter to the buried rib waveguide of the AWGR, which could not be measured directly.

To improve overall device performance, the total loss in the AWGR region should be reduced. The higher than desired loss in our structure is likely due to two main factors. First, because the input and output lines and the arrayed waveguides are defined with the buried rib structure which etches into the waveguide layer, sidewall roughness created during the dry etch can result in high scattering losses. This would especially affect the input and output waveguides to and from the star couplers,

Fig. 10. BER measurements for several input wavelength converters at 40 Gb/s monitored from a constant output port. Back-to-back BER measurements are also included for the converted wavelengths.

which range in length from 6 to 10 mm. A future, more compact AWGR design similar to that of [27] could reduce these passive losses and increase the overall output power from the router. The design of [27] is also promising because it would eliminate the separate dry etch step currently used for the AWGR, thus reducing fabrication complexity. A second contribution to our AWGR loss is the coupling loss between the star couplers and the arrayed waveguide. Our lithographic capabilities should allow us to bring the waveguides separation down from their current value of 0.8 to about 0.5  $\mu$ m in a future design to help reduce these coupling losses.

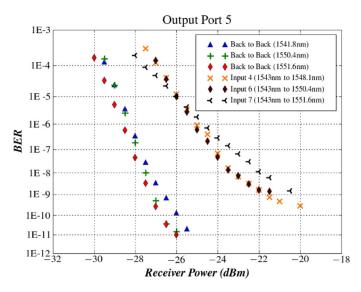

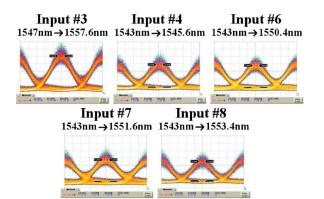

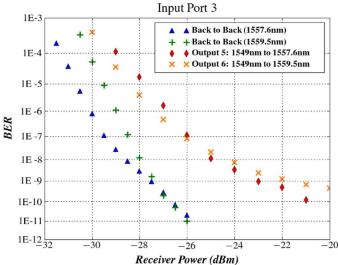

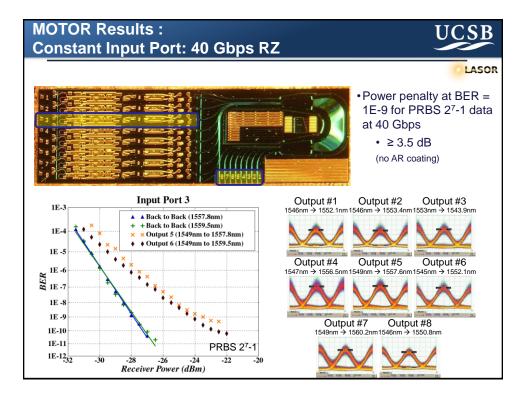

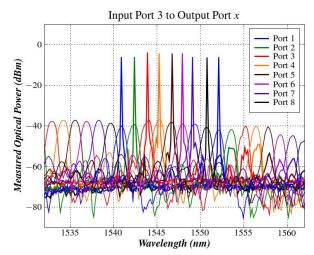

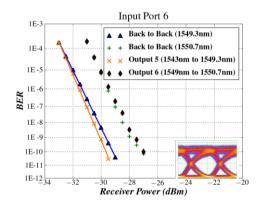

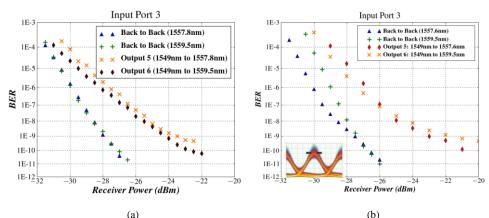

### VI. WAVELENGTH CONVERTER AND ROUTING RESULTS AND DISCUSSION

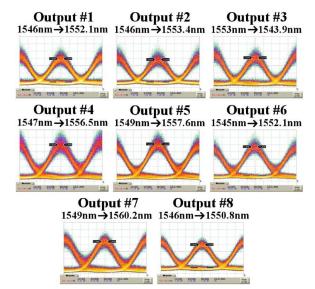

Once the tuning characteristics of the SG-DBR are known, 40-Gb/s wavelength conversion and channel switching in the RZ data format can be achieved. Typical bias levels used for wavelength conversion are given in Table I. Figs. 10 and 11 show BER results and the associated eye diagrams for wavelength conversion from multiple-input channels through a constant output port, respectively. Eye diagrams are not shown for three of the eight wavelength converters. Although the diode yield was close to 100%, two channels did not function because of a random ridge defect in the MZI region. The other missing channel was damaged during testing. However, since the working channels have an identical structure, there are no inherent wavelength converter design issues and all channels are expected to work with an improved fabrication yield. Next, we measured the BER for wavelength conversion through different output ports using a constant input channel (Fig. 12). Open eye diagrams were also obtained for all eight output ports using a single-input channel (Fig. 13).

These results demonstrate the tunable routing ability of the MOTOR chip, as the input data to one input port can be directed to different output ports by simply changing the SG-DBR mirror biasing conditions. Figs. 10 and 12 also demonstrate that BERs

Fig. 11. Open eyes diagrams for several input wavelength converters at 40 Gb/s from a constant output port.

Fig. 12. BER measurements for a single-input wavelength converter at 40 Gb/s monitored from different output ports. Back-to-back BER measurements are also included for the converted wavelengths.

Fig. 13. Open eyes diagrams for a single-input wavelength converter at 40 Gb/s from all eight output ports.

below 1E-9 are possible for the combined wavelength conversion and routing process. The measured power penalties at this

TABLE I WAVELENGTH CONVERTER TYPICAL BIASES

| Component           | Bias (mA) |

|---------------------|-----------|

| Preamplifer SOAs    | 110-140   |

| Booster SOAs        | 30-60     |

| MZI SOAs            | 210-290   |

| MZI Phase Modulator | 0-5       |

| SG-DBR Gain         | 100-110   |

| SG-DBR Front Mirror | 0-25      |

| SG-DBR Back Mirror  | 0-25      |

BER range from approximately 4.5 to 7.0 dB (depending on the input port).

The noise floor and high-power penalty seen in these results are likely attributable to two main factors. First, the tested MOTOR chip was not antireflective (AR) coated. Additionally, given the high power of the SG-DBR, other minor reflections may exist in the device during operation. These reflections within the chip might occur at the transitions between the three different waveguide architectures. In future MOTOR designs, optimized AR coatings are planned to address this reflection issue.

Second, we measured a clear pattern dependence during wavelength conversion due to saturation in the preamplifier SOAs made from the centered MQW band edge. In order to provide enough gain to the input signal to deplete the MZI SOAs of carriers and modulate the MZI, the preamplifier SOAs had to operate in the nonlinear gain regime. This resulted in pattern distortion effects and an increased BER. In order to overcome these limitations, a more complex preamplifier structure will be required. One possible approach to increase the saturation power of the preamplifiers would involve combining the short centered MQW SOA in our device with a second MQW SOA section regrown some distance above the center of the waveguide as in [28]. This method has demonstrated SOAs with gains as high as 15 dB and output saturation powers of >19 dBm, but the additional regrowth could have a negative impact on device yield.

The results reported here apply only to single-channel operation. Moving to multiple-channel operation will not only require more elaborate biasing and fiber coupling schemes, but will also increase the expected power penalty for the combined process of wavelength conversion and switching. One key reason for this is expected to be the increased heating in the device with all diodes biased. This increased heating can lead to signal degradation and reduced output power due to thermal crosstalk effects in both the wavelength converters and the AWGR. Efficient heat sinking will therefore be vital to overall performance.

### VII. POWER CONSUMPTION CONSIDERATIONS

The wavelength conversion and switching functions of the MOTOR chip come at a relatively low cost in terms of power consumption. Under normal operating conditions, the single-channel drive power is less than 2 W, giving an overall expected drive power of less than 16 W for eight-channel operation. However, additional power is necessary for TEC cooling. In our current testing configuration, the TEC requires ~0.5 W to maintain a single channel at the 16 °C temperature used during testing. In

a real application, the chip would be packaged with more efficient heat sinking (i.e., flip-chip bonding) with all channels operating simultaneously. The operating temperature would also likely be higher to match that of other system elements. Therefore, although the results reported here are promising, further work to characterize TEC demands under these conditions is needed before accurate comparisons with electronic router components can be drawn.

### VIII. CONCLUSION

We report the demonstration of the first InP  $8 \times 8$  MOTOR capable of 40-Gb/s operation per port with BERs below 1E-9. The device represents one of the most densely integrated InP chips ever reported, with more than 200 integrated functions and power penalty as low as 4.5 dB at 40 Gb/s. Under normal operating conditions, the per channel power consumption is less than 2 W. Improved power penalty is expected with future designs employing AR coatings and optimized preamplifier SOAs.

#### ACKNOWLEDGMENT

The authors would like to thank J. Mack and H. Poulsen for their assistance with test equipment. They would also like to thank LandMark Optoelectronics Corporation for the base epitaxial growth and III–V Lab for the cladding regrowth. Device fabrication was done at the UCSB nanofabrication facility, part of the National Science Foundation (NSF) funded NNIN network.

#### REFERENCES

- D. Wolfson, V. Lal, M. L. Mašanović, H. N. Poulsen, C. Coldren, G. Epps, D. Civello, P. Donner, and D. J. Blumenthal, "All-optical asynchronous variable-length optically labelled 40 Gbps packet switch," presented at the Eur. Conf. Opt. Commun., Glasgow, Scotland, 2005.

- [2] R. Nagarajan, M. Kato, J. Pleumeekers, P. Evans, D. Lambert, A. Chen, V. Dominic, A. Mathur, P. Chavarkar, M. Missey, A. Dentai, S. Hurtt, J. Bäck, R. Muthiah, S. Murthy, R. Salvatore, C. Joyner, J. Rossi, R. Schneider, M. Ziari, H.-S. Tsai, J. Bostak, M. Kauffman, S. Pennypacker, T. Butrie, M. Reffle, D. Mehuys, M. Mitchell, A. Nilsson, S. Grubb, F. Kish, and D. Welch, "Large-scale photonic integrated circuits for long-haul transmission and switching," J. Opt. Netw., vol. 6, pp. 102–111, Feb. 2007.

- [3] M. K. Smit, E. A. J. M. Bente, M. T. Hill, F. Karouta, X. J. M. Leijtens, Y. S. Oei, J. J. G. M. van der Tol, R. Notzel, P. M. Koenraad, H. S. Dorren, H. de Waardt, A. M. J. Koonen, and G. D. Khoe, "Current status and prospects of photonic IC technology," in *Proc. IEEE Conf. Indium Phosphide Related Mater.*, 2007, pp. 3–6.

- [4] R. Kaiser and H. Heidrich, "Optoelectronic/photonic integrated circuits on InP between technological feasibility and commercial success," *IEICE Trans. Electron.*, vol. E85-C, pp. 970–981, Apr. 2002.

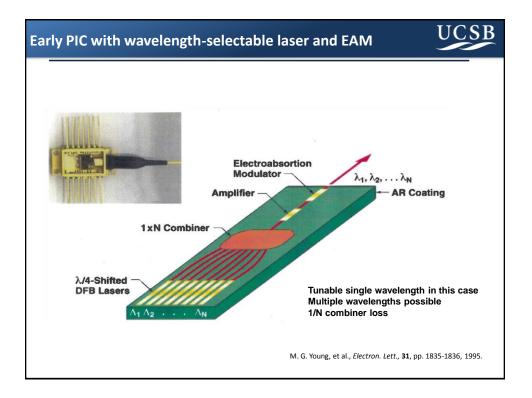

- [5] J. Raring and L. Coldren, "40-Gb/s widely tunable transceivers," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 1, pp. 3–14, Jan./Feb. 2007.

- [6] M. L. Mašanović, V. Lal, J. A. Summers, J. S. Barton, E. J. Skogen, L. G. Rau, L. A. Coldren, and D. J. Blumenthal, "Widely tunable monolithically integrated all-optical wavelength converters in InP," *J. Lightw. Technol.*, vol. 23, no. 3, pp. 1350–1362, Mar. 2005.

- [7] V. Lal, M. L. Mašanović, J. A. Summers, G. Fish, and D. J. Blumenthal, "Monolithic wavelength converters for high-speed packet-switched optical networks," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 1, pp. 47–57, Jan./Feb. 2007.

- [8] P. Bernasconi, L. Zhang, W. Yang, N. Sauer, L. L. Buhl, J. H. Sinsky, I. Kang, S. Chandrasekhar, and D. T. Neilson, "Monolithically integrated 40-Gb/s switchable wavelength converter," *J. Lightw. Technol.*, vol. 24, no. 1, pp. 71–76, Jan. 2006.

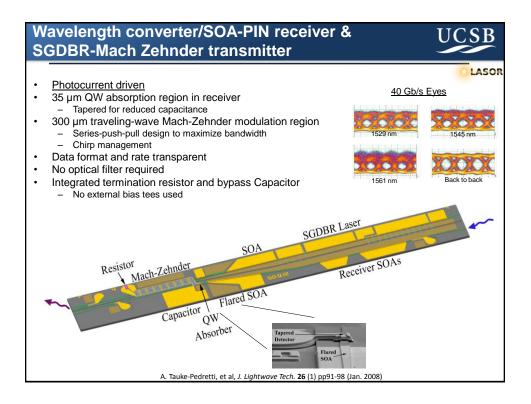

- [9] M. Dummer, J. Klamkin, A. Tauke-Pedretti, and L. Coldren, "40 Gb/s widely tunable wavelength converter with a photocurrent-driven highimpedance TW-EAM and SGDBR laser," in *Proc. IEEE Int. Semicond. Laser Conf.*, 2008, pp. 145–146.

- [10] C. G. P. Herben, C. G. M. Vreeburg, D. H. P. Maat, X. J. M. Leijtens, Y. S. Oei, F. H. Groen, J. W. Pedersen, P. Demeester, and M. K. Smit, "A compact integrated InP-based single-phasar optical crossconnect," *IEEE Photon. Technol. Lett.*, vol. 10, no. 5, pp. 678–680, May 1998.

- [11] C. Vreeburg, T. Uitterdijk, Y. Oei, M. Smit, F. Groen, E. Metaal, P. Demeester, and H. Frankena, "First InP-based reconfigurable integrated add-drop multiplexer," *IEEE Photon. Technol. Lett.*, vol. 9, no. 2, pp. 188–190, Feb. 1997.

- [12] N. Kikuchi, Y. Shibata, H. Okamoto, Y. Kawaguchi, S. Oku, H. Ishii, Y. Yoshikuni, and Y. Tohmori, "Monolithically integrated 64-channel WDM channel selector with novel configuration," *Electron. Lett.*, vol. 38, pp. 331–332, 2002.

- [13] R. Nagarajan, C. H. Joyner, R. P. Schneider, Jr., J. S. Bostak, T. Butrie, A. G. Dentai, V. G. Dominic, P. W. Evans, M. Kato, M. Kauffman, D. J. H. Lambert, S. K. Mathis, A. Mathur, R. H. Miles, M. L. Mitchell, M. J. Missey, S. Murthy, A. C. Nilsson, F. H. Peters, S. C. Pennypacker, J. L. Pleumeekers, R. A. Salvatore, R. K. Schlenker, R. B. Taylor, H.-S. Tsai, M. F. Van Leeuwen, J. Webjorn, M. Ziari, D. Perkins, J. Singh, S. G. Grubb, M. S. Reffle, D. G. Mehuys, F. A. Kish, and D. F. Welch, "Large scale photonic integrated circuits," *IEEE J. Sel. Topics Quantum Electron.*, vol. 11, no. 1, pp. 50–65, Jan./Feb. 2005.

- [14] "Infinera's 400 Gb/s PIC Sets New Record for Integration," Mar. 23, 2009 [Online]. Available: http://www.infinera.com/j7/servlet/ NewsItem?newsItemID=150, [Accessed: July 15, 2009]

- [15] D. F. Welch, F. A. Kish, R. Nagarajan, C. H. Joyner, R. P. Schneider, V. G. Dominic, M. L. Mitchell, S. G. Grubb, T.-K. Chiang, D. Perkins, and A. C. Nilsson, "The realization of large-scale photonic integrated circuits and the associated impact on fiber-optic communication systems," *J. Lightw. Technol.*, vol. 24, no. 12, pp. 4674–4683, Dec. 2006.

- [16] J. Mack, H. Poulsen, E. Burmeister, B. Stamenic, G. Kurczveil, J. Bowers, and D. Blumenthal, "Demonstration of contention resolution for labeled packets at 40 Gb/s using autonomous optical buffers," in *Proc. Opt. Fiber Commun. Conf.*, San Diego, CA, Mar. 2009, OMU2.

- [17] E. Burmeister, J. Mack, H. Poulsen, M. L. Mašanović, B. Stamenic, D. Blumenthal, and J. Bowers, "Photonic integrated circuit optical buffer for packet-switched networks," *Opt. Exp.*, vol. 17, pp. 6629–6635, Apr. 13, 2009.

- [18] D. J. Blumenthal, B.-E. Olsson, G. Rossi, T. E. Dimmick, L. Rau, M. L. Mašanović, O. Lavrova, R. Doshi, O. Jerphagnon, J. E. Bowers, V. Kaman, L. A. Coldren, and J. Barton, "All-optical label swapping networks and technologies," *J. Lightw. Technol.*, vol. 18, no. 12, pp. 2058–2075, Dec. 2000.

- [19] V. Lal, M. L. Mašanović, J. Summers, L. Coldren, and D. Blumenthal, "Performance optimization of an InP-based widely tunable all-optical wavelength converter operating at 40 Gb/s," *IEEE Photon. Technol. Lett.*, vol. 4, no. 2, pp. 577–579, Feb. 2006.

- [20] V. Lal, "Monolithic wavelength converters for high-speed packet switched optical networks," Ph.D. dissertation, Dept. Electr. Eng., Univ. California, Santa Barbara, CA, 2006.

- [21] V. Jayaraman, Z. Chuang, and L. Coldren, "Theory, design, and performance of extended tuning range semiconductor lasers with sampled gratings," *IEEE J. Quantum Electron.*, vol. 29, no. 6, pp. 1824–1834, Jun. 1993.

- [22] M. Smit and C. van Dam, "PHASAR-based WDM-devices: Principles, design and applications," *IEEE J. Sel. Topics Quantum Electron.*, vol. 2, no. 2, pp. 236–250, Jun. 1996.

- [23] E. Skogen, J. Barton, S. Denbaars, and L. Coldren, "A quantum-wellintermixing process for wavelength-agile photonic integrated circuits," *IEEE J. Sel. Topics Quantum Electron.*, vol. 8, no. 4, pp. 863–869, Jul./ Aug. 2002.

- [24] J. Shim, M. Yamaguchi, P. Delansay, and M. Kitamura, "Refractive index and loss changes produced by current injection in InGaAs(P)-InGaAsP multiple quantum-well (MQW) waveguides," *IEEE J. Sel. Topics Quantum Electron.*, vol. 1, no. 2, pp. 408–415, Jun. 1995.

- [25] S. C. Nicholes, M. L. Mašanović, J. Barton, E. J. Norberg, E. Lively, B. Jevremovic, L. A. Coldren, and D. J. Blumenthal, "Novel application of quantum well intermixing implant buffer layer to enable high-density photonic integrated circuits in InP," presented at the IEEE Conf. Indium Phosphide Related Mater., Newport Beach, CA, May 10–14, 2009, paper WB1. 2.

- [26] L. Ketelsen and R. Kazarinov, "Carrier loss in InGaAsP-InP lasers grown by hydride CVD," *IEEE J. Quantum Electron.*, vol. 31, no. 5, pp. 811–813, May 1995.

- [27] J. Besten, M. Dessens, C. Herben, X. Leijtens, F. Groen, M. Leys, and M. Smit, "Low-loss, compact, and polarization independent PHASAR demultiplexer fabricated by using a double-etch process," *IEEE Photon. Technol. Lett.*, vol. 14, no. 1, pp. 62–64, Jan. 2002.

- [28] J. Raring, E. Skogen, M. L. Mašanović, S. DenBaars, and L. Coldren, "Demonstration of high saturation power/high gain SOAs using quantum well intermixing based integration platform," *Electron. Lett.*, vol. 41, pp. 1345–1346, 2005.

**Steven C. Nicholes** received the B.S. degree in chemical engineering from Brigham Young University, Provo, UT, in 2005. He is currently working toward the Ph.D. degree in materials at the University of California, Santa Barbara.

His research interests include the design and fabrication of widely tunable semiconductor lasers and semiconductor optical amplifiers for large scale photonic integrated circuits. He is also interested in MOCVD growth and has designed novel epitaxial structures for low-loss optical propagation and

high-polarization extinction.

**Milan L. Mašanović** (S'98–M'04) received the Dipl. Ing. degree from the School of Electrical Engineering, University of Belgrade, Belgrade, Yugoslavia, in 1998 and the M.S. and Ph.D. degrees from the University of California at Santa Barbara, Santa Barbara, in 2000 and 2004, respectively, all in electrical engineering.

He is currently a Research Scientist at the University of California at Santa Barbara. He is also a founder of Freedom Photonics, a photonic integration company in Santa Barbara, CA. He is the author

or coauthor of more than 70 research papers. His current research interests include InP photonic integration related to applications in packet-switched optical networks.

Dr. Mašanović was the recipient of the 2004 IEEE Lasers and Electro-Optics Society Graduate Student Fellowship Award and the 2003 Best Student Paper Award at the Indium Phosphide and Related Materials Conference.

**Biljana Jevremović** received the Dipl. Ing. degree in metallurgy, and completed graduate coursework for M.S. degree in metallurgy of nonferrous metals at the School of Technology and Metallurgy, University of Belgrade, Belgrade, Yugoslavia, in 1994 and 1999.

She worked as a Research Assistant at the Institute for Technology of Nuclear and Other Mineral Row Materials (ITNMS). She worked as a Device Fabrication Technician. She is currently a Senior Development Engineer at the University of California at Santa Barbara.

**Erica Lively** (S'06) received the B.S. degree in electrical engineering from the University of Idaho, Moscow, in 2005 and the M.S. degree in electrical engineering from the University of California at Santa Barbara, Santa Barbara, in 2007, where she is currently working towards the Ph.D. degree.

Her research interests include the fabrication and simulation of metamaterials, slow light devices, and nanophotonic devices. She is also interested in the societal implications of science and technology.

**Larry A. Coldren** (S'67–M'72–SM'77–F'82) received the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, in 1972.

He is the Fred Kavli Professor of Optoelectronics and Sensors at the University of California at Santa Barbara, Santa Barbara. After 13 years in the research area at Bell Laboratories, he joined University of California at Santa Barbara in 1984 where he now holds appointments in Materials and Electrical & Computer Engineering, and is Director of the Optoelectronics Technology Center. In 1990, he cofounded Optical

Concepts, later acquired as Gore Photonics, to develop novel VCSEL technology; and in 1998, he cofounded Agility Communications, later acquired by JDSU, to develop widely tunable integrated transmitters. At Bell Labs, he initially worked on waveguided surface-acoustic-wave signal processing devices and coupled-resonator filters. He later developed tunable coupled-cavity lasers using novel reactive-ion etching (RIE) technology that he created for the then new InP-based materials. At University of California at Santa Barbara he continued work on multiple-section tunable lasers, in 1988 inventing the widely tunable multielement mirror concept, which is now used in some JDSU products. During the late 1980s, he also developed efficient vertical-cavity multiple-quantum-well modulators, which led to novel vertical-cavity surface-emitting laser (VCSEL) designs that provided unparalleled levels of performance. He continues to be active in developing new photonic integrated circuit (PIC) and VCSEL technology, including the underlying materials growth and fabrication techniques. In recent years, for example, he has been involved in the creation of efficient all-epitaxial InP-based and high-modulation speed GaAs-based VCSELs as well as a variety of InP-based PICs incorporating numerous optical elements for widely tunable integrated transmitters, receivers, and wavelength converters operating up to 40 Gb/s. He has authored or coauthored over 1000 journal and conference papers, seven book chapters, one textbook, and has been issued 63 patents.

Prof. Coldren has presented dozens of invited and plenary talks at major conferences. He is a Fellow of the Optical Society of America (OSA) and the Institution of Electrical Engineers (IEE), the recipient of the 2004 John Tyndall Award, and a member of the National Academy of Engineering.

Daniel J. Blumenthal (S'91–M'93–SM'97–F'03) received the B.S.E.E. degree from the University of Rochester, Rochester, NY, in 1981, the M.S.E.E. degree from Columbia University, New York, in 1988, and the Ph.D. degree from the University of Colorado, Boulder, in 1993, all in electrical engineering.

In 1981, he was with StorageTek, Louisville, CO, and during 1993–1997 he was an Assistant Professor at the School of Electrical and Computer Engineering, Georgia Institute of Technology, At-

lanta. He is currently a Professor in the Department of Electrical and Computer Engineering, University of California at Santa Barbara (UCSB), Santa Barbara. He is the Director of the LASOR Center at UCSB, a project funded by the Defense Advanced Research Projects Agency Data in the Optical Domain Network (DOD-N) Program and currently serves on the Board of Directors for National LambdaRail. He is also the Cofounder of Calient Networks and Packet Photoncis, LLC. He is the author or coauthor of over 300 research papers and is the coauthor of *Tunable Laser Diodes and Related Optical Sources* (New York: IEEE-Wiley, 2005). His current research interests include optical communications, photonic packet-switched and all-optical networks, all-optical wavelength conversion, ultrafast communications systems, integrated photonic circuits, and nanophotonic technologies.

Dr. Blumenthal was the recipient of the 1999 Presidential Early Career Award for Scientists and Engineers from the White House, the 1994 National Science Foundation Young Investigator Award, and the 1997 Office of Naval Research Young Investigator Program Award. He has served as an Associate Editor for the IEEE PHOTONICS TECHNOLOGY LETTERS and the IEEE TRANSACTIONS ON COMMUNICATIONS, as a Guest Editor for the JOURNAL OF LIGHTWAVE TECHNOLOGY special issue on photonic packet switching systems and the IEEE JOURNAL OF SELECTED AREAS IN COMMUNICATIONS special issue on high-performance optical/electronic switches/routers for high-speed Internet. He has served as the General Program Chair for the 2001 Optical Society of America (OSA) Topical Meeting on Photonics in Switching and as Program Chair for the 1999 Meeting on Photonics in Switching. He has also served on numerous other technical program committees. He is a Fellow of the Optical Society of America (OSA).

## High-Performance Photonic Integrated Circuits (PICs)

## Larry A. Coldren

OFC Tutorial OWD1

March 24, 2010

## A Typical Data Center

- > 30 MW power requirements

- Require many Gb/s of bandwidth—justifies 100Gb-Ethernet

| 640 Gbps MOT       | TOR UCSB                                                                                                                                         |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>↓</b> Wavelengt | h Converter Array Arrayed-Waveguide Grating Router                                                                                               |

|                    |                                                                                                                                                  |

| Benefits of inte   | grated solution:                                                                                                                                 |

| Size               | Smaller device footprint     Smaller rack space for increased bandwidth                                                                          |

| Power              | <ul> <li>No power required in passive AWGR (free switching—no transistors)</li> <li>Lower power consumption with all-optical approach</li> </ul> |

| Cost               | <ul><li>Reduced packaging and system costs</li><li>Fewer fiber alignments</li></ul>                                                              |

| Performance        | Increased reliability                                                                                                                            |

|                    |                                                                                                                                                  |

# QWI For Multiple-Band Edges/Single Growth

- <u>Strategy</u>:

- 1. Centered MQW base structure

- 2. Quantum-well intermixing for active/passive definition

- 3. Single blanket cladding regrowth

- <u>Trade-offs</u>:

- Limited total number of regrowths → need multiple waveguide architectures

- Efficient active diodes → higher passive losses due to Zn in cladding

- Efficient high-gain, low-saturation power elements → nonlinear preamplifiers

- 4. Polarization sensitivity

- Active InP-based photonic ICs can be created with size, weight, power and system performance metrics superior to discrete solutions in many situations. However, cost can only be less if the market size is sufficient.

- Close integration of control/feedback electronics will be desirable in many future PIC applications

- Coherent approaches will be greatly enabled by the use of photonic Integration, and numerous sensor applications may be enabled in addition to higher-spectral-efficiency communications.

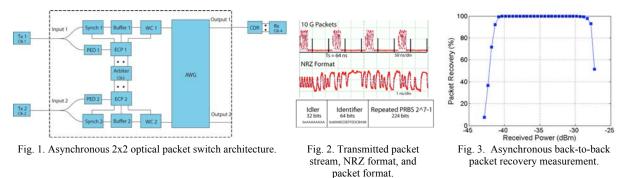

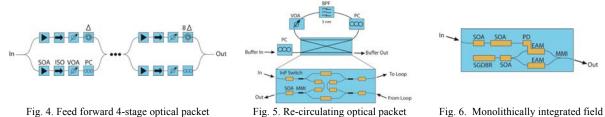

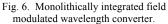

# Asynchronous 2x2 Optical Packet Synchronization, Buffering, and Forwarding

# John P. Mack, Kimchau N. Nguyen, John M. Garcia, Emily F. Burmeister, Matt M. Dummer, Henrik N. Poulsen, Biljana Stamenic, Geza Kurczveil, Kurtis Hollar, Larry A. Coldren, John E. Bowers, and Daniel J. Blumenthal

Electrical and Computer Engineering Department, University of California, Santa Barbara jmack@ece.ucsb.edu

**Abstract:** We demonstrate the first asynchronous 2x2 optical packet switch capable of synchronizing, buffering, and forwarding 10 Gb/s packets generated from independent transmitters with better than 99% packet recovery measured using a burst mode receiver. ©2010 Optical Society of America

OCIS codes: (060.1810) Buffers, couplers, routers, switches, and multiplexers; (230.4480) Optical amplifiers

#### 1. Introduction

Optical packet switching provides a means of communication that is flexible, scalable, and high capacity [1]. Asynchronous operation of routers is the key to scaling large networks where multiple independent nodes are used, each with their own packet and bit-level clock sources. This causes inherent timing uncertainties on the clock and packet-level due to the frequency drift between plesiochronous clocks [2]. These uncertainties create unique challenges to optical technologies and switch architectures. In order to utilize synchronous buffer architectures with asynchronous packets, incoming packets must be aligned to the packet timeslots of the switch through the use of synchronizers. Packets are then synchronously loaded and unloaded from buffers to resolve temporal collisions of packets destined for the same output port [3]. Synchronous buffering is a critical component of any router as synchronization guarantees minimal uncertainty of the location of packets within buffers and allows for efficient time division multiplexing of packets onto output ports. In addition to optical buffering, the switch also requires photonic technologies to forward packets to different output ports. Optical synchronization, buffering, and forwarding approaches have been demonstrated individually with low power penalties at 40 Gb/s [4-6]. Previously, asynchronous optical forwarding of labeled optical packets was demonstrated for high bit-rate variable length 40 Gb/s payloads based on lower bit-rate 10 Gb/s labels [7]. End-to-end asynchronous optical transmission, forwarding, and detection have been shown for Internet protocol (IP) packets adapted to a labeled optical packet format for 12.5 Gb/s payloads with 3.125 Gb/s labels [8]. Asynchronous transmission, buffering, forwarding, and detection of 160 Gb/s payloads based on all-optical label processing has also been demonstrated [9]. In all of the previous work, contention of optical packets was pre-engineered using a single transmitter. The results reported here are the first demonstrations of synchronizing, buffering, and forwarding asynchronous optical packets generated by multiple independent sources.

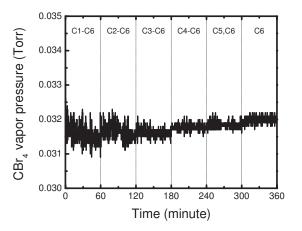

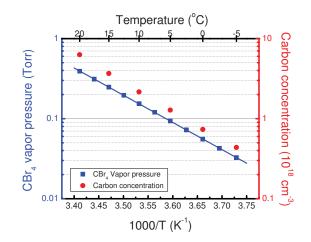

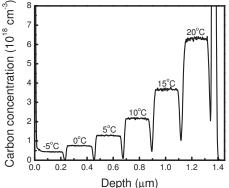

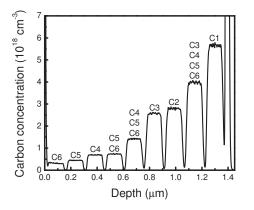

#### 2. Architecture